### **Chapter 1 Objectives**

- Know the difference between computer organization and computer architecture.

- Understand units of measure common to computer systems.

- Appreciate the evolution of computers.

- Understand the computer as a layered system.

- Be able to explain the von Neumann architecture and the function of basic computer components.

### 1.1 Overview

# -

2

# Why study computer organization and architecture?

- Design better programs, including system software such as compilers, operating systems, and device drivers.

- Optimize program behavior.

- Evaluate (benchmark) computer system performance.

- Understand time, space, and price tradeoffs.

### 1.1 Overview

- Computer organization

- Encompasses all physical aspects of computer systems.

- E.g., circuit design, control signals, memory types.

- How does a computer work?

### Computer architecture

- Logical aspects of system implementation as seen by the programmer.

- E.g., instruction sets, instruction formats, data types, addressing modes.

- How do I design a computer?

### **1.2 Computer Components**

4

- There is no clear distinction between matters related to computer organization and matters relevant to computer architecture.

- Principle of Equivalence of Hardware and Software:

- Anything that can be done with software can also be done with hardware, and anything that can be done with hardware can also be done with software.\*

- \* Assuming speed is not a concern.

### **1.2 Computer Components**

6

5

• At the most basic level, a computer is a device consisting of three pieces:

A processor to interpret and execute programs

A memory to store both data and programs

A mechanism for transferring data to and from the

outside world.

### Measures of capacity and speed:

- Kilo- (K) = 1 thousand =  $10^3$  and  $2^{10}$

- Mega- (M) = 1 million =  $10^6$  and  $2^{20}$

- Giga- (G) = 1 billion =  $10^9$  and  $2^{30}$

- Tera- (T) = 1 trillion =  $10^{12}$  and  $2^{40}$

- Peta- (P) = 1 quadrillion =  $10^{15}$  and  $2^{50}$

Whether a metric refers to a power of ten or a power of two <u>typically</u> depends upon what is being measured.

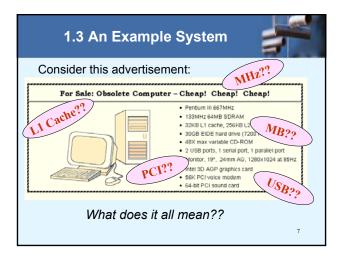

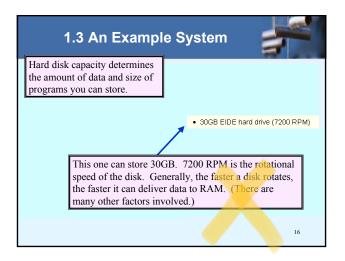

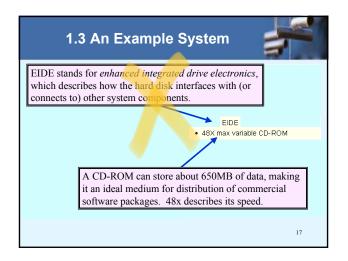

### 1.3 An Example System

- Hertz = clock cycles per second (frequency)

- 1MHz = 1,000,000Hz

- Processor speeds are measured in MHz or GHz.

- Byte = a unit of storage

- 1KB =  $2^{10}$  = 1024 Bytes

- $-1MB = 2^{20} = 1,048,576$  Bytes

- Main memory (RAM) is measured in MB

- Disk storage is measured in GB for small systems, TB for large systems.

### Measures of time and space:

- Milli- (m) = 1 thousandth =  $10^{-3}$

- Micro- ( $\mu$ ) = 1 millionth = 10<sup>-6</sup>

- Nano- (n) = 1 billionth =  $10^{-9}$

- Pico- (p) = 1 trillionth =  $10^{-12}$

- Femto- (f) = 1 quadrillionth =  $10^{-15}$

### 1.3 An Example System

10

- Millisecond = 1 thousandth of a second

Hard disk drive access times are often 10 to 20 milliseconds.

- Nanosecond = 1 billionth of a second

- Main memory access times are often 50 to 70 nanoseconds.

- Micron (micrometer) = 1 millionth of a meter

Circuits on computer chips are measured in microns.

# 1.3 An Example System

11

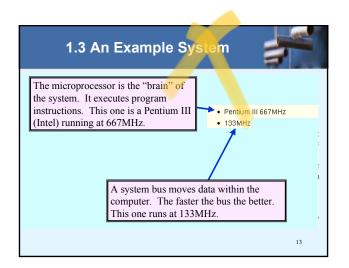

- We note that cycle time is the reciprocal of clock frequency.

- A bus operating at 133MHz has a cycle time of 7.52 nanoseconds:

133,000,000 cycles/second = 7.52 ns/cycle

Now back to the advertisement ...

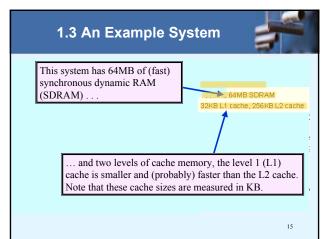

- Computers with large main memory capacity can run larger programs with greater speed than computers having small memories.

- RAM is an acronym for random access memory. Random access means that memory contents can be accessed directly if you know its location.

- Cache is a type of temporary memory that can be accessed faster than RAM.

- Serial ports send data as a series of pulses along one or two data lines.

- Parallel ports send data as a single pulse along at least eight data lines.

- USB, universal serial bus, is an intelligent serial interface that is self-configuring. (It supports "plug and play.")

Throughout the remainder of this book you will see how these components work and how they interact with software to make complete computer systems.

### This statement raises two important questions:

What assurance do we have that computer components will operate as we expect?

And what assurance do we have that computer components will operate together?

### 1.4 Standards Organizations

22

- There are many organizations that set computer hardware standards-- to include the interoperability of computer components.

- Throughout this book, and in your career, you will encounter many of them.

- Some of the most important standardssetting groups are . . .

### **1.4 Standards Organizations**

-

- The Institute of Electrical and Electronic Engineers (IEEE)

- Promotes the interests of the worldwide electrical engineering community.

- Establishes standards for computer components, data representation, and signaling protocols, among many other things.

### 1.4 Standards Organizations

- The International Telecommunications Union (ITU)

- Concerns itself with the interoperability of telecommunications systems, including data communications and telephony.

- National groups establish standards within their respective countries:

- The American National Standards Institute (ANSI)

- The British Standards Institution (BSI)

### **1.4 Standards Organizations**

-

25

- The International Organization for Standardization (ISO)

- Establishes worldwide standards for everything from screw threads to photographic film.

- Is influential in formulating standards for computer hardware and software, including their methods of manufacture.

- Note: ISO is **not** an acronym. ISO comes from the Greek, *isos*, meaning "equal."

### **1.5 Historical Development**

26

- To fully appreciate the computers of today, it is helpful to understand how things got the way they are.

- The evolution of computing machinery has taken place over several centuries.

- In modern times computer evolution is usually classified into four generations according to the salient technology of the era.

We note that many of the following dates are approximate.

### **1.5 Historical Development**

- · Generation Zero: Mechanical Calculating Machines (1642 - 1945)

- Calculating Clock Wilhelm Schickard (1592 1635).

- Pascaline Blaise Pascal (1623 1662).

- Difference Engine Charles Babbage (1791 1871), also designed but never built the Analytical Engine.

- Punched card tabulating machines Herman Hollerith (1860 - 1929).

Hollerith cards were commonly used for computer input well into the 1970s.

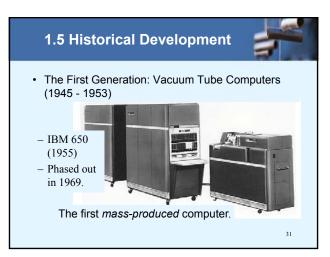

# **1.5 Historical Development**

- · The First Generation: Vacuum Tube Computers (1945 - 1953)

- Atanasoff Berry 15 Computer (1937 -1938) solved systems of linear equations.

John Atanasoff and Clifford Berry of Iowa State University.

29

28

### **1.5 Historical Development**

- The First Generation: Vacuum Tube Computers (1945 - 1953)

- Electronic Numerical Integrator and Computer (ENIAC)

- John Mauchly and J. Presper Eckert

- University of Pennsylvania, 1946

# <section-header><section-header><section-header><text><text><list-item><list-item><list-item><list-item><list-item><list-item>

### **1.5 Historical Development**

- The Third Generation: Integrated Circuit Computers (1965 - 1980)

- IBM 360

- DEC PDP-8 and PDP-11

- Cray-1 supercomputer

... and many

- others.

### **1.5 Historical Development**

- The Fourth Generation: VLSI Computers (1980 - ????)

- Very large scale integrated circuits (VLSI) have more than 10,000 components per chip.

Enabled the creation of microprocessors.

34

The first was the 4-bit Intel 4004.

Later versions, such as the 8080, 8086, and 8088 spawned the idea of "personal computing."

# **1.5 Historical Development**

- Moore's Law (1965)

- Gordon Moore, Intel founder

- "The density of transistors in an integrated circuit will double every year."

- · Contemporary version:

- "The density of silicon chips doubles every 18 months."

But this "law" cannot hold forever ...

### **1.5 Historical Development**

35

- Rock's Law

- Arthur Rock, Intel financier

- "The cost of capital equipment to build semiconductors will double every four years."

- In 1968, a new chip plant cost about \$12,000.

At the time, \$12,000 would buy a nice home in the suburbs. An executive earning \$12,000 per year was "making a very comfortable living."

### **1.5 Historical Development**

### · Rock's Law

In 2003, a chip plant under construction will cost over \$2.5 billion.

> \$2.5 billion is more than the gross domestic product of some small countries, including Belize, Bhutan, and the Republic of Sierra Leone.

> > 37

38

For Moore's Law to hold, Rock's Law must fall, or vice versa. But no one can say which will give out first.

### 1.6 The Computer Level Hierarchy

- Computers consist of many things besides chips.

- Before a computer can do anything worthwhile, it must also use software.

- Writing complex programs requires a "divide and conquer" approach, where each program module solves a smaller problem.

- Complex computer systems employ a similar technique through a series of virtual machine layers.

### 1.6 The Computer Level Hierarchy

- Each virtual machine layer is an abstraction of the level below it.

- The machines at each level execute their own particular instructions, calling upon machines at lower levels to perform tasks as required.

- Computer circuits ultimately carry out the work.

# 1.6 The Computer Level Hierarchy

- · Level 6: The User Level

- Program execution and user interface level.

- The level with which we are most familiar.

- Level 5: High-Level Language Level

- The level with which we interact when we write programs in languages such as C, Pascal, Lisp, and Java.

# 1.6 The Computer Level Hierarchy

- · Level 4: Assembly Language Level

- Acts upon assembly language produced from Level 5, as well as instructions programmed directly at this level.

- Level 3: System Software Level

- Controls executing processes on the system.

- Protects system resources.

- Assembly language instructions often pass through Level 3 without modification.

### 41

40

# **1.6 The Computer Level Hierarchy**

- Level 2: Machine Level

- Also known as the Instruction Set Architecture (ISA) Level.

- Consists of instructions that are particular to the architecture of the machine.

- Programs written in machine language need no compilers, interpreters, or assemblers.

# 1.6 The Computer Level Hierarchy

- · Level 1: Control Level

- A control unit decodes and executes instructions and moves data through the system.

- Control units can be *microprogrammed* or *hardwired*.

- A microprogram is a program written in a lowlevel language that is implemented by the hardware.

- Hardwired control units consist of hardware that directly executes machine instructions.

# 1.6 The Computer Level Hierarchy

- Level 0: Digital Logic Level

- This level is where we find digital circuits (the chips).

- Digital circuits consist of gates and wires.

- These components implement the mathematical logic of all other levels.

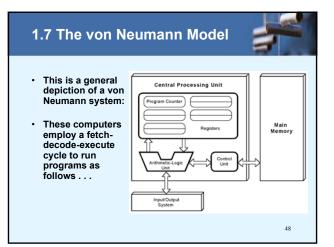

### 1.7 The von Neumann Model

- On the ENIAC, all programming was done at the digital logic level.

- Programming the computer involved moving plugs and wires.

43

### 1.7 The von Neumann Model

- Inventors of the ENIAC, John Mauchley and J. Presper Eckert, conceived of a computer that could store instructions in memory.

- The invention of this idea has since been ascribed to a mathematician, John von Neumann, who was a contemporary of Mauchley and Eckert.

- Stored-program computers have become known as von Neumann Architecture systems.

### 1.7 The von Neumann Model

1

46

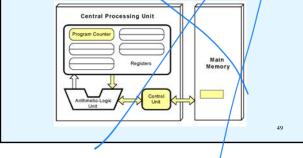

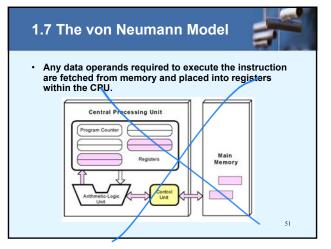

- Today's stored-program computers have the following characteristics:

- Three hardware systems:

- A central processing unit (CPU)

- A main memory system

- An I/O system

- The capacity to carry out sequential instruction processing.

- A single data path between the CPU and main memory.

- This single path is known as the von Neumann bottleneck.

### 1.7 The von Neumann Model

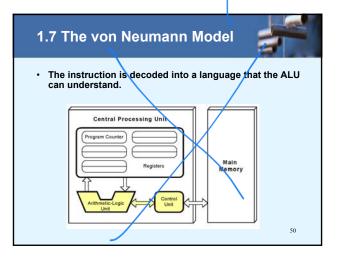

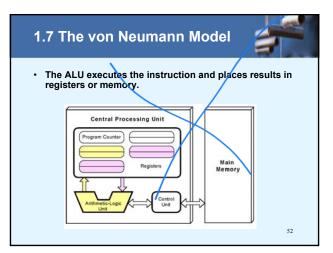

• The control unit fetches the next instruction from memory using the program counter to determine where the instruction is located.

### 1.8 Non-von Neumann Models

- Conventional stored-program computers have undergone many incremental improvements over the years.

- These improvements include adding specialized buses, floating-point units, and cache memories, to name only a few.

- But enormous improvements in computational power require departure from the classic von Neumann architecture.

53

54

Adding processors is one approach.

### **1.8 Non-von Neumann Models**

- In the late 1960s, high-performance computer systems were equipped with dual processors to increase computational throughput.

- In the 1970s supercomputer systems were introduced with 32 processors.

- Supercomputers with 1,000 processors were built in the 1980s.

- In 1999, IBM announced its Blue Gene system containing over 1 million processors.

### 1.8 Non-von Neumann Models

- Parallel processing is only one method of providing increased computational power.

- More radical systems have reinvented the fundamental concepts of computation.

- These advanced systems include genetic computers, quantum computers, and dataflow systems.

- At this point, it is unclear whether any of these systems will provide the basis for the next generation of computers.

55

56

### Conclusion

- This chapter has given you an overview of the subject of computer architecture.

- You should now be sufficiently familiar with general system structure to guide your studies throughout the remainder of this course.

- Subsequent chapters will explore many of these topics in great detail.

### **Chapter 2 Objectives**

- Understand the fundamentals of numerical data representation and manipulation in digital computers.

- Master the skill of converting between various radix systems.

- Understand how errors can occur in computations because of overflow and truncation.

# **Chapter 2 Objectives**

- Gain familiarity with the most popular character codes.

- Become aware of the differences between how data is stored in computer memory, how it is transmitted over telecommunication lines, and how it is stored on disks.

- Understand the concepts of error detecting and correcting codes.

### **2.1 Introduction**

- A *bit* is the most basic unit of information in a computer.

- It is a state of "on" or "off" in a digital circuit.

- Sometimes these states are "high" or "low" voltage instead of "on" or "off.."

- A byte is a group of eight bits.

- A byte is the smallest possible *addressable* unit of computer storage.

- The term, "addressable," means that a particular byte can be retrieved according to its location in memory.

4

5

### **2.1 Introduction**

- A word is a contiguous group of bytes.

- Words can be any number of bits or bytes.

- Word sizes of 16, 32, or 64 bits are most common.

- In a word-addressable system, a word is the smallest addressable unit of storage.

- A group of four bits is called a *nibble* (or *nybble*).

- Bytes, therefore, consist of two nibbles: a "high-order nibble," and a "low-order" nibble.

# 2.2 Positional Numbering Systems

- Bytes store numbers when the position of each bit represents a power of 2.

- The binary system is also called the base-2 system.

- Our decimal system is the base-10 system. It uses powers of 10 for each position in a number.

- Any integer quantity can be represented exactly using any base (or *radix*).

### 2.2 Positional Numbering Systems

• The decimal number 947 in powers of 10 is:

$9\times10^{\,2}+4\times10^{\,1}+7\times10^{\,0}$

• The decimal number 5836.47 in powers of 10 is:

$\begin{array}{l} 5\times10^{\;3}+8\times10^{\;2}+3\times10^{\;1}+6\times10^{\;0}\\ +\,4\times10^{\;-1}+7\times10^{\;-2} \end{array}$

### 2.2 Positional Numbering Systems

• The binary number 11001 in powers of 2 is:

$1 \times 2^{\,4} + 1 \times 2^{\,3} + 0 \times 2^{\,2} \ + 0 \times 2^{\,1} + 1 \times 2^{\,0}$

= 16 + 8 + 0 + 0 + 1 = 25

• When the radix of a number is something other than 10, the base is denoted by a subscript.

- Sometimes, the subscript 10 is added for emphasis:

$11001_2 = 25_{10}$

### 2.3 Decimal to Binary Conversions

- Because binary numbers are the basis for all data representation in digital computer systems, it is important that you become proficient with this radix system.

- Your knowledge of the binary numbering system will enable you to understand the operation of all computer components as well as the design of instruction set architectures.

- In a previous slide, we said that every integer value can be represented exactly using any radix system.

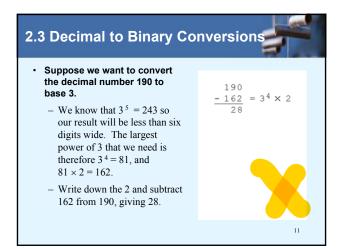

- You can use either of two methods for radix conversion: the subtraction method and the division remainder method.

- The subtraction method is more intuitive, but cumbersome. It does, however reinforce the ideas behind radix mathematics.

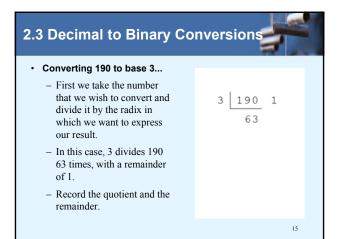

- Another method of converting integers from decimal to some other radix uses division.

- This method is mechanical and easy.

- It employs the idea that successive division by a base is equivalent to successive subtraction by powers of the base.

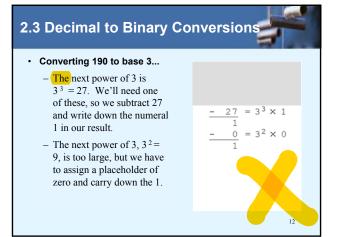

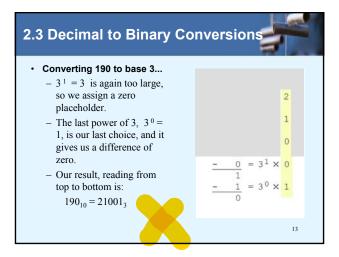

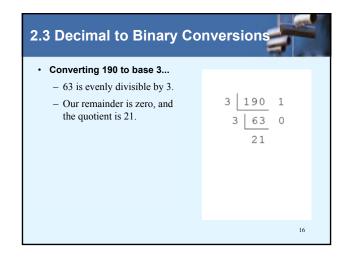

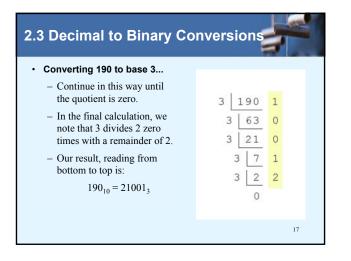

- Let's use the division remainder method to again convert 190 in decimal to base 3.

- Fractional values can be approximated in all base systems.

- Unlike integer values, fractions do not necessarily have exact representations under all radices.

- The quantity ½ is exactly representable in the binary and decimal systems, but is not in the ternary (base 3) numbering system.

- Fractional decimal values have nonzero digits to the right of the decimal point.

- Fractional values of other radix systems have nonzero digits to the right of the radix point.

- Numerals to the right of a radix point represent negative powers of the radix:

$\begin{array}{rl} 0.47_{10} = \ 4 \times 10^{-1} + 7 \times 10^{-2} \\ 0.11_2 = \ 1 \times 2^{-1} + 1 \times 2^{-2} \\ = \ 1/2 & + \ 1/4 \\ = & 0.5 & + & 0.25 = & 0.75 \end{array}$

19

20

### 2.3 Decimal to Binary Conversions

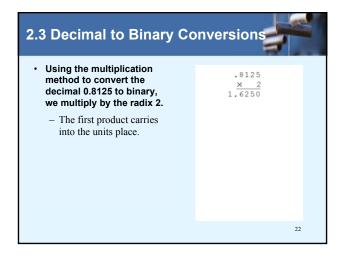

- As with whole-number conversions, you can use either of two methods: a subtraction method and an easy multiplication method.

- The subtraction method for fractions is identical to the subtraction method for whole numbers.

Instead of subtracting positive powers of the target radix, we subtract negative powers of the radix.

- We always start with the largest value first, *n*<sup>-1</sup>, where *n* is our radix, and work our way along using larger negative exponents.

### 2.3 Decimal to Binary Conversions · The calculation to the right is an example of using the subtraction 0.8125 $-0.5000 = 2^{-1} \times 1$ method to convert the decimal 0.8125 to binary. 0.3125 $-0.2500 = 2^{-2} \times 1$ - Our result, reading from 0.0625 top to bottom is: $0 = 2^{-3} \times 0$ $0.8125_{10} = 0.1101_2$ 0.0625 $-0.0625 = 2^{-4} \times 1$ - Of course, this method 0 works with any base, not just binary. 21

| 2.3 Decimal to Binary Conversions                                                                                                                                                |                                                                                                                                     |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Converting 0.8125 to binary</li> <li>Ignoring the value in the units<br/>place at each step, continue<br/>multiplying each fractional<br/>part by the radix.</li> </ul> | $ \begin{array}{r} .8125 \\ \times & 2 \\ 1.6250 \\ .6250 \\ \times & 2 \\ 1.2500 \\ .2500 \\ \times & 2 \\ 0.5000 \\ \end{array} $ |  |  |

|                                                                                                                                                                                  | 23                                                                                                                                  |  |  |

| 2.3 Decimal to Binary Co                                                                                                                                                                                                                                                                                                                                             | onversions                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| <ul> <li>Converting 0.8125 to binary</li> <li>You are finished when the product is zero, or until you have reached the desired number of binary places.</li> <li>Our result, reading from top to bottom is:</li> <li>0.8125<sub>10</sub> = 0.1101<sub>2</sub></li> <li>This method also works with any base. Just use the target radix as the multiplier.</li> </ul> | $ \begin{array}{r}         .8125 \\                                    $ |

|                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                       |

- The binary numbering system is the most important radix system for digital computers.

- However, it is difficult to read long strings of binary numbers-- and even a modestly-sized decimal number becomes a very long binary number.

- For example:  $11010100011011_2 = 13595_{10}$

- For compactness and ease of reading, binary values are usually expressed using the hexadecimal, or base-16, numbering system.

### 2.3 Decimal to Binary Conversions

- The hexadecimal numbering system uses the numerals 0 through 9 and the letters A through F.

- The decimal number 12 is  $B_{16}$ .

- The decimal number 26 is  $1A_{16}$ .

- It is easy to convert between base 16 and base 2, because 16 = 2<sup>4</sup>.

- Thus, to convert from binary to hexadecimal, all we need to do is group the binary digits into groups of four.

A group of four binary digits is called a hextet

# 2.3 Decimal to Binary Conversions • Using groups of hextets, the binary number $11010100011011_2$ (= $13595_{10}$ ) in hexadecimal is: 0011 0101 0001 1011 3 5 1 B

Octal (base 8) values are derived from binary by using groups of three bits (8 = 2<sup>3</sup>):

Octal was very useful when computers used six-bit words.

27

25

- The conversions we have so far presented have involved only positive numbers.

- To represent negative values, computer systems allocate the high-order bit to indicate the sign of a value.

- The high-order bit is the leftmost bit in a byte. It is also called the most significant bit.

- The remaining bits contain the value of the number.

# 2.4 Signed Integer Representation

- There are three ways in which signed binary numbers may be expressed:

- Signed magnitude,

- One's complement and

- Two's complement.

- In an 8-bit word, signed magnitude representation places the absolute value of the number in the 7 bits to the right of the sign bit.

### 2.4 Signed Integer Representation

- For example, in 8-bit signed magnitude, positive 3 is: 00000011

- Negative 3 is: 10000011

- Computers perform arithmetic operations on signed magnitude numbers in much the same way as humans carry out pencil and paper arithmetic.

- Humans often ignore the signs of the operands while performing a calculation, applying the appropriate sign after the calculation is complete.

28

- Binary addition is as easy as it gets. You need to know only four rules:

- The simplicity of this system makes it possible for digital circuits to carry out arithmetic operations.

- We will describe these circuits in Chapter 3.

Let's see how the addition rules work with signed magnitude numbers . . .

31

###

### 2.4 Signed Integer Representation

- Example:

- Using signed magnitude binary arithmetic, find the sum of 75 and 46.

- Just as in decimal arithmetic, we find the sum starting with the rightmost bit and work left.

0 1001011

0 + 0101110

### • Example: - Using signed magnitude binary arithmetic, find the 0 1001011 sum of 75 and 46. 0 + 0101110 • In the second bit, we have a carry, so we note it above the third bit.

01

34

| 2.4 Signed Integer Representation                                                                                                                                               |                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| <ul> <li>Example:</li> <li>Using signed magnitude<br/>binary arithmetic, find the<br/>sum of 75 and 46.</li> <li>The third and fourth bits also<br/>give us carries.</li> </ul> | $ \begin{array}{c} 0 & 1001011 \\ 0 & \pm 0101110 \\  & \pm 0101110 \\  & 1001 \end{array} $ |  |

|                                                                                                                                                                                 | 35                                                                                           |  |

### 2.4 Signed Integer Representation

- Using signed magnitude binary arithmetic, find the sum of 75 and 46.

1 1 1 0 1001011 0 + 0101110 1111001 0

• Once we have worked our way through all eight bits, we are done.

> In this example, we were careful careful to pick two values whose sum would fit into seven bits. If that is not the case, we have a problem.

### • Example:

- Using signed magnitude binary arithmetic, find the sum of 107 and 46.

- We see that the carry from the seventh bit *overflows* and is discarded, giving us the erroneous result; 107 + 46 = 25.

37

38

# 2.4 Signed Integer Representation

The signs in signed magnitude representation work just like the signs in pencil and paper arithmetic.

$\begin{array}{c}

1 & 0101110 \\

1 & + 0011001 \\

1 & 1000111

\end{array}$

- Example: Using signed magnitude binary arithmetic, find the sum of - 46 and - 25.

- Because the signs are the same, all we do is add the numbers and supply the negative sign when we are done.

# 2.4 Signed Integer Representation

- Mixed sign addition (or subtraction) is done the same way.

- Example: Using signed magnitude binary arithmetic, find the sum of 46 and - 25.

- The sign of the result gets the sign of the number that is larger.

- Note the "borrows" from the second and sixth bits.

- Signed magnitude representation is easy for people to understand, but it requires complicated computer hardware.

- Another disadvantage of signed magnitude is that it allows two different representations for zero: positive zero and negative zero.

- For these reasons (among others) computers systems employ complement systems for numeric value representation.

# 2.4 Signed Integer Representation

- In complement systems, negative values are represented by some difference between a number and its base.

- In diminished radix complement systems, a negative value is given by the difference between the absolute value of a number and one less than its base.

- In the binary system, this gives us one's complement. It amounts to little more than flipping the bits of a binary number.

### 2.4 Signed Integer Representation

- For example, in 8-bit one's complement, positive 3 is: 00000011

- Negative 3 is: 11111100 - In one's complement, as with signed magnitude,

- negative values are indicated by a 1 in the high order bit.

Complement systems are useful because they eliminate the need for special circuitry for subtraction. The difference of two values is found by adding the minuend to the complement of the subtrahend.

40

- With one's complement addition, the carry bit is "carried around" and added to the sum.

- Example: Using one's complement binary arithmetic, find the sum of 48 and - 19

We note that 19 in one's complement is 00010011, so -19 in one's complement is: 11101100.

00110000

11101100

00011100

+ 1

00011101

43

44

# 2.4 Signed Integer Representation

- Although the "end carry around" adds some complexity, one's complement is simpler to implement than signed magnitude.

- But it still has the disadvantage of having two different representations for zero: positive zero and negative zero.

- Two's complement solves this problem.

- Two's complement is the radix complement of the binary numbering system.

### 2.4 Signed Integer Representation

- · To express a value in two's complement:

- If the number is positive, just convert it to binary and you're done.

- If the number is negative, find the one's complement of the number and then add 1.

- Example:

- In 8-bit one's complement, positive 3 is: 00000011

- Negative 3 in one's complement is: 11111100

- Adding 1 gives us -3 in two's complement form: 11111101.

- · With two's complement arithmetic, all we do is add our two binary numbers. Just discard any carries emitting from the high order bit.

- Example: Using one's complement binary arithmetic, find the sum of 48 and - 19.

### 1)-4 00110000 + 11101101 00011101

We note that 19 in one's complement is: 00010011, so -19 in one's complement is: and -19 in two's complement is:

11101100,

46

47

11 111 01101011

10011001

48

+ 00101110

# 2.4 Signed Integer Representation

- · When we use any finite number of bits to represent a number, we always run the risk of the result of our calculations becoming too large to be stored in the computer.

- While we can't always prevent overflow, we can always detect overflow.

- · In complement arithmetic, an overflow condition is easy to detect.

# 2.4 Signed Integer Representation

- Using two's complement binary arithmetic, find the sum of 107 and 46.

- We see that the nonzero carry from the seventh bit overflows into the sign bit, giving us the erroneous result: 107 + 46 = -103.

Rule for detecting two's complement overflow: When the "carry in" and the "carry out" of the sign bit differ, overflow has occurred.

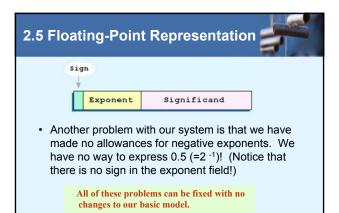

### 2.5 Floating-Point Representation

- The signed magnitude, one's complement, and two's complement representation that we have just presented deal with integer values only.

- Without modification, these formats are not useful in scientific or business applications that deal with real number values.

- Floating-point representation solves this problem.

### 2.5 Floating-Point Representation

- If we are clever programmers, we can perform floating-point calculations using any integer format.

- This is called *floating-point emulation*, because floating point values aren't stored as such, we just create programs that make it seem as if floatingpoint values are being used.

- Most of today's computers are equipped with specialized hardware that performs floating-point arithmetic with no special programming required.

### 2.5 Floating-Point Representation

- Floating-point numbers allow an arbitrary number of decimal places to the right of the decimal point.

- For example:  $0.5 \times 0.25 = 0.125$

- They are often expressed in scientific notation.

- For example:  $0.125 = 1.25 \times 10^{-1}$

- $5,000,000 = 5.0 \times 10^6$

49

- Computers use a form of scientific notation for floating-point representation

- Numbers written in scientific notation have three components:

| Sign | Manti  | Exponer            | nt |

|------|--------|--------------------|----|

| 3    | + 1.25 | × 10 <sup>-1</sup> |    |

|      |        |                    |    |

| 2.5 Floating-Point                                                                                                            | Representation |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

| <ul> <li>Computer representation of a floating-point<br/>number consists of three fixed-size fields:</li> <li>Sign</li> </ul> |                |  |  |  |  |

| Exponent                                                                                                                      | Significand    |  |  |  |  |

| This is the standard arrangement of these fields.                                                                             |                |  |  |  |  |

|                                                                                                                               | 53             |  |  |  |  |

| 2.5 Floating-Point Representation                                                                               |

|-----------------------------------------------------------------------------------------------------------------|

| Sign                                                                                                            |

| Exponent Significand                                                                                            |

| The one-bit sign field is the sign of the stored value.                                                         |

| <ul> <li>The size of the exponent field, determines the<br/>range of values that can be represented.</li> </ul> |

| <ul> <li>The size of the significand determines the precision<br/>of the representation.</li> </ul>             |

| 21 | gn       |             |

|----|----------|-------------|

| 1  |          |             |

|    | Exponent | Significand |

- The IEEE-754 *single precision* floating point standard uses an 8-bit exponent and a 23-bit significand.

- The IEEE-754 *double precision* standard uses an 11-bit exponent and a 52-bit significand.

For illustrative purposes, we will use a 14-bit model with a 5-bit exponent and an 8-bit significand.

# 2.5 Floating-Point Representation Sign Exponent Significand The significand of a floating-point number is always preceded by an implied binary point. Thus, the significand always contains a fractional

- Thus, the significand always contains a fractional binary value.

- The exponent indicates the power of 2 to which the significand is raised.

# 2.5 Floating-Point Representation

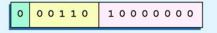

- · Example:

- Express 32<sub>10</sub> in the simplified 14-bit floating-point model.

- We know that 32 is 2<sup>5</sup>. So in (binary) scientific notation 32 = 1.0 x 2<sup>5</sup> = 0.1 x 2<sup>6</sup>.

- Using this information, we put 110 (= 6<sub>10</sub>) in the exponent field and 1 in the significand as shown.

55

- The illustrations shown at the right are all equivalent representations for 32 using our simplified model.

- Not only do these synonymous representations waste space, but they can also cause confusion.

| C | 0 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|-----|---|---|---|---|---|---|---|---|---|---|---|

| • | 0 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| • | ) 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 6 | 1   | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

# 2.5 Floating-Point Representation

- To resolve the problem of synonymous forms, we will establish a rule that the first digit of the significand must be 1. This results in a unique pattern for each floating-point number.

- In the IEEE-754 standard, this 1 is implied meaning that a 1 is assumed after the binary point.

- By using an implied 1, we increase the precision of the representation by a power of two. (Why?)

In our simple instructional model, we will use no implied bits.

- To provide for negative exponents, we will use a *biased exponent*.

- A bias is a number that is approximately midway in the range of values expressible by the exponent. We subtract the bias from the value in the exponent to determine its true value.

- In our case, we have a 5-bit exponent. We will use 16 for our bias. This is called *excess-16* representation.

- In our model, exponent values less than 16 are negative, representing fractional numbers.

# 2.5 Floating-Point Representation

- Express 32<sub>10</sub> in the revised 14-bit floating-point model.

- We know that 32 = 1.0 x 2<sup>5</sup> = 0.1 x 2<sup>6</sup>.

- To use our excess 16 biased exponent, we add 16 to 6, giving 22<sub>10</sub> (=10110<sub>2</sub>).

- · Graphically:

# 0 10110 1000000

# 2.5 Floating-Point Representation

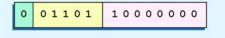

- · Example:

- Express 0.0625<sub>10</sub> in the revised 14-bit floating-point model.

- We know that 0.0625 is 2<sup>-4</sup>. So in (binary) scientific notation 0.0625 = 1.0 x 2<sup>-4</sup> = 0.1 x 2<sup>-3</sup>.

- To use our excess 16 biased exponent, we add 16 to -3, giving 13<sub>10</sub> (=01101<sub>2</sub>).

61

### · Example:

- Express -26.625<sub>10</sub> in the revised 14-bit floating-point model.

- We find  $26.625_{10}$  = 11010.1012. Normalizing, we have:  $26.625_{10}$  = 0.11010101 x 2  $^5.$

- To use our excess 16 biased exponent, we add 16 to 5, giving 21<sub>10</sub> (=10101<sub>2</sub>). We also need a 1 in the sign bit.

| 1 10101 11010101 | 1    |

|------------------|------|

|                  | 1774 |

64

65

# 2.5 Floating-Point Representation

- The IEEE-754 single precision floating point standard uses bias of 127 over its 8-bit exponent.

- An exponent of 255 indicates a special value.

- If the significand is zero, the value is  $\pm$  infinity.

- If the significand is nonzero, the value is NaN, "not a number," often used to flag an error condition.

- The double precision standard has a bias of 1023 over its 11-bit exponent.

- The "special" exponent value for a double precision number is 2047, instead of the 255 used by the single precision standard.

# 2.5 Floating-Point Representation

- Both the 14-bit model that we have presented and the IEEE-754 floating point standard allow two representations for zero.

- Zero is indicated by all zeros in the exponent and the significand, but the sign bit can be either 0 or 1.

- This is why programmers should avoid testing a floating-point value for equality to zero.

- Negative zero does not equal positive zero.

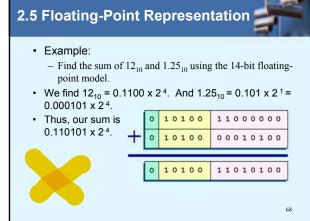

- Floating-point addition and subtraction are done using methods analogous to how we perform calculations using pencil and paper.

- The first thing that we do is express both operands in the same exponential power, then add the numbers, preserving the exponent in the sum.

- If the exponent requires adjustment, we do so at the end of the calculation.

67

69

# 2.5 Floating-Point Representation

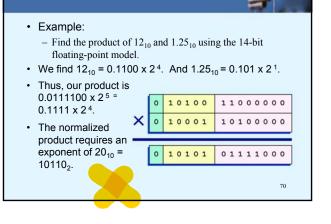

- Floating-point multiplication is also carried out in a manner akin to how we perform multiplication using pencil and paper.

- We multiply the two operands and add their exponents.

- If the exponent requires adjustment, we do so at the end of the calculation.

# 2.5 Floating-Point Representation

- No matter how many bits we use in a floating-point representation, our model must be finite.

- The real number system is, of course, infinite, so our models can give nothing more than an approximation of a real value.

- At some point, every model breaks down, introducing errors into our calculations.

- By using a greater number of bits in our model, we can reduce these errors, but we can never totally eliminate them.

# 2.5 Floating-Point Representation

- Our job becomes one of reducing error, or at least being aware of the possible magnitude of error in our calculations.

- We must also be aware that errors can compound through repetitive arithmetic operations.

- For example, our 14-bit model cannot exactly represent the decimal value 128.5. In binary, it is 9 bits wide:

10000000.1<sub>2</sub> = 128.5<sub>10</sub>

72

• When we try to express 128.5<sub>10</sub> in our 14-bit model, we lose the low-order bit, giving a relative error of:

$$\frac{128.5 - 128}{128} \approx 0.39\%$$

• If we had a procedure that repetitively added 0.5 to 128.5, we would have an error of nearly 2% after only four iterations.

# 2.5 Floating-Point Representation

- Floating-point errors can be reduced when we use operands that are similar in magnitude.

- If we were repetitively adding 0.5 to 128.5, it would have been better to iteratively add 0.5 to itself and then add 128.5 to this sum.

- In this example, the error was caused by loss of the low-order bit.

- · Loss of the high-order bit is more problematic.

# 2.5 Floating-Point Representation

- Floating-point overflow and underflow can cause programs to crash.

- Overflow occurs when there is no room to store the high-order bits resulting from a calculation.

- Underflow occurs when a value is too small to store, possibly resulting in division by zero.

Experienced programmers know that it's better for a program to crash than to have it produce incorrect, but plausible, results.

73

### 2.6 Character Codes

1

76

- Calculations aren't useful until their results can be displayed in a manner that is meaningful to people.

- We also need to store the results of calculations, and provide a means for data input.

- Thus, human-understandable characters must be converted to computer-understandable bit patterns using some sort of character encoding scheme.

# 2.6 Character Codes

- As computers have evolved, character codes have evolved.

- Larger computer memories and storage devices permit richer character codes.

- The earliest computer coding systems used six bits.

- Binary-coded decimal (BCD) was one of these early codes. It was used by IBM mainframes in the 1950s and 1960s.

# 2.6 Character Codes

-

- In 1964, BCD was extended to an 8-bit code, Extended Binary-Coded Decimal Interchange Code (EBCDIC).

- EBCDIC was one of the first widely-used computer codes that supported upper *and* lowercase alphabetic characters, in addition to special characters, such as punctuation and control characters.

- EBCDIC and BCD are still in use by IBM mainframes today.

### 2.6 Character Codes

- Other computer manufacturers chose the 7-bit ASCII (American Standard Code for Information Interchange) as a replacement for 6-bit codes.

- While BCD and EBCDIC were based upon punched card codes, ASCII was based upon telecommunications (Telex) codes.

- Until recently, ASCII was the dominant character code outside the IBM mainframe world.

79

80

### 2.6 Character Codes

- Many of today's systems embrace Unicode, a 16bit system that can encode the characters of every language in the world.

- The Java programming language, and some operating systems now use Unicode as their default character code.

- The Unicode codespace is divided into six parts. The first part is for Western alphabet codes, including English, Greek, and Russian.

### 2.6 Character Codes

- The Unicode codespace allocation is shown at the right.

- The lowest-numbered Unicode characters comprise the ASCII code.

- The highest provide for user-defined codes.

| Character<br>Types | Language                                                                       | Number of<br>Characters | Hexadecima<br>Values |

|--------------------|--------------------------------------------------------------------------------|-------------------------|----------------------|

| Alphabets          | Latin, Greek,<br>Cyrillic, etc.                                                | 8192                    | 0000<br>to<br>1FFF   |

| Symbols            | Dingbats,<br>Mathematical,<br>etc.                                             | 4096                    | 2000<br>to<br>2FFF   |

| СЈК                | Chinese,<br>Japanese,<br>and Korean<br>phonetic<br>symbols and<br>punctuation. | 4096                    | 3000<br>to<br>3FFF   |

| Han                | Unified Chinese,<br>Japanese, and<br>Korean                                    | 40,960                  | 4000<br>to<br>DFFF   |

|                    | Han Expansion                                                                  | 4096                    | E000<br>to<br>EFFF   |

| User<br>Defined    |                                                                                | 4095                    | F000<br>to<br>FFFE   |

|                    |                                                                                |                         | 81                   |

# 2.7 Codes for Data Recording And Transmission

- When character codes or numeric values are stored in computer memory, their values are unambiguous.

- This is not always the case when data is stored on magnetic disk or transmitted over a distance of more than a few feet.

- Owing to the physical irregularities of data storage and transmission media, bytes can become garbled.

- Data errors are reduced by use of suitable coding methods as well as through the use of various errordetection techniques.

82

83

# 2.7 Codes for Data Recording And Transmission

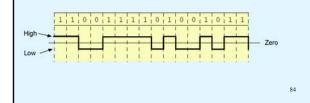

- To transmit data, pulses of "high" and "low" voltage are sent across communications media.

- To store data, changes are induced in the magnetic polarity of the recording medium.

- These polarity changes are called *flux reversals*.

- The period of time during which a bit is transmitted, or the area of magnetic storage within which a bit is stored is called a *bit cell*.

# 2.7 Codes for Data Recording And Transmission

- The simplest data recording and transmission code is the non-return-to-zero (NRZ) code.

- NRZ encodes 1 as "high" and 0 as "low."

- The coding of OK (in ASCII) is shown below.

# 2.7 Codes for Data Recording And Transmission

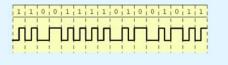

- The problem with NRZ code is that long strings of zeros and ones cause synchronization loss.

- Non-return-to-zero-invert (NRZI) reduces this synchronization loss by providing a transition (either low-to-high or high-to-low) for each binary 1.

| 1 1 0 | 0 1 1 1 1 | 0 1 0 1 1 |

|-------|-----------|-----------|

| Ψ÷    |           |           |

|       | 1111      |           |

85

86

87

# 2.7 Codes for Data Recording And Transmission

- Although it prevents loss of synchronization over long strings of binary ones, NRZI coding does nothing to prevent synchronization loss within long strings of zeros.

- Manchester coding (also known as phase modulation) prevents this problem by encoding a binary one with an "up" transition and a binary zero with a "down" transition.

1 1 0 0 1 1 1 1 1 0 1 0 0 1 0 1 1

# 2.7 Codes for Data Recording And Transmission

- For many years, Manchester code was the dominant transmission code for local area networks.

- It is, however, wasteful of communications capacity because there is a transition on every bit cell.

- A more efficient coding method is based upon the frequency modulation (FM) code. In FM, a transition is provided at each cell boundary. Cells containing binary ones have a mid-cell transition.

# 2.7 Codes for Data Recording And Transmission

- At first glance, FM is worse than Manchester code, because it requires a transition at each cell boundary.

- If we can eliminate some of these transitions, we would have a more economical code.

- Modified FM does just this. It provides a cell boundary transition only when adjacent cells contain zeros.

- An MFM cell containing a binary one has a transition in the middle as in regular FM.

# 2.7 Codes for Data Recording And Transmission

- The main challenge for data recording and transmission is how to retain synchronization without chewing up more resources than necessary.

- Run-length-limited, RLL, is a code specifically designed to reduce the number of consecutive ones and zeros.

- Some extra bits are inserted into the code.

- But even with these extra bits RLL is remarkably efficient.

90

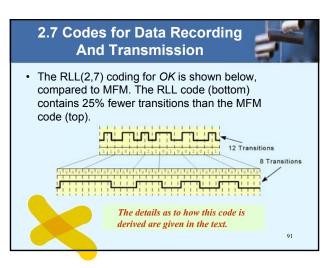

# 2.7 Codes for Data Recording And Transmission

- An RLL(d,k) code dictates a minimum of d and a maximum of k consecutive zeros between any pair of consecutive ones.

- RLL(2,7) has been the dominant disk storage coding method for many years.

- An RLL(2,7) code contains more bit cells than its corresponding ASCII or EBCDIC character.

- However, the coding method allows bit cells to be smaller, thus closer together, than in MFM or any other code.

- It is physically impossible for any data recording or transmission medium to be 100% perfect 100% of the time over its entire expected useful life.

- As more bits are packed onto a square centimeter of disk storage, as communications transmission speeds increase, the likelihood of error increases-sometimes geometrically.

- Thus, error detection and correction is critical to accurate data transmission, storage and retrieval.

# 2.8 Error Detection and Correction

- Check digits, appended to the end of a long number can provide some protection against data input errors.

- The last character of UPC barcodes and ISBNs are check digits.

- Longer data streams require more economical and sophisticated error detection mechanisms.

- Cyclic redundancy checking (CRC) codes provide error detection for large blocks of data.

- Checksums and CRCs are examples of systematic error detection.

- In systematic error detection a group of error control bits is appended to the end of the block of transmitted data.

- This group of bits is called a syndrome,

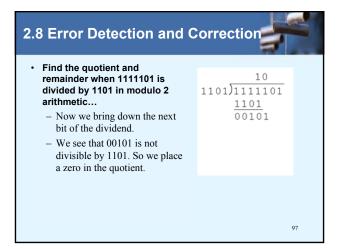

- CRCs are polynomials over the modulo 2 arithmetic field.

The mathematical theory behind modulo 2 polynomials is beyond our scope. However, we can easily work with it without knowing its theoretical underpinnings.

94

95

# 2.8 Error Detection and Correction

- Modulo 2 arithmetic works like clock arithmetic.

- In clock arithmetic, if we add 2 hours to 11:00, we get 1:00.

- In modulo 2 arithmetic if we add 1 to 1, we get 0. The addition rules couldn't be simpler:

0 + 0 = 0 0 + 1 = 11 + 0 = 1 1 + 1 = 0

You will fully understand why modulo 2 arithmetic is so handy after you study digital circuits in Chapter 3.

2.8 Error Detection and Correction · Find the quotient and 1 remainder when 1111101 is 1101)1111101 divided by 1101 in modulo 2 arithmetic. 1101 - As with traditional division 0010 we note that the dividend s divisible once by the We place the divisor under the dividend and perform modulo 2 subtraction. 96

| 2.8 Error Detection and Correction                                                                                                                                                                                           |                                                                                                                         |    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| <ul> <li>Find the quotient and<br/>remainder when 1111101 is<br/>divided by 1101 in modulo 2<br/>arithmetic</li> <li>1010 is divisible by 1101 in<br/>modulo 2.</li> <li>We perform the modulo 2<br/>subtraction.</li> </ul> | $   \begin{array}{r} 101 \\     1101 \\     1111101 \\     1101 \\     01010 \\     1101 \\     0111 \\   \end{array} $ |    |  |  |  |

|                                                                                                                                                                                                                              |                                                                                                                         | 98 |  |  |  |

| 2.8 Error Detection and Correction                                                                                     |                                                                                                 |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| <ul> <li>Find the quotient and<br/>remainder when 1111101 is<br/>divided by 1101 in modulo 2<br/>arithmetic</li> </ul> | $     \begin{array}{r} 1011 \\     1101 \\     1101 \\     1101   \end{array} $                 |  |  |  |  |

| <ul> <li>We find the quotient is 1011,<br/>and the remainder is 0010.</li> </ul>                                       | 001010                                                                                          |  |  |  |  |

| <ul> <li>This procedure is very useful<br/>to us in calculating CRC<br/>syndromes.</li> </ul>                          | $     \begin{array}{r}       011111 \\       \underline{1101} \\       0010     \end{array}   $ |  |  |  |  |

| Note: The divisor in this ex<br>to a modulo 2 polynomial                                                               |                                                                                                 |  |  |  |  |

| 2.8 Error Detection and C                                                                                                                                                                                                                                                                                                                                                                                                            | orrection                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Suppose we want to transmit the information string: 1111101.</li> <li>The receiver and sender decide to use the (arbitrary) polynomial pattern, 1101.</li> <li>The information string is shifted (left by one position less than the value of positions in the divisor.</li> <li>The remainder is found through modulo 2 division (at right) and added to the information string: 1111101000 + 111 = 1111101111.</li> </ul> | $ \begin{array}{r} 1011011\\1101)1111101000\\ \underline{1101}\\001010\\ \underline{1101}\\01111\\ \underline{1101}\\001000\\ \underline{1101}\\01010\\ \underline{1101}\\01010\\ \underline{1101}\\1101\end{array} \end{array} $ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0111                                                                                                                                                                                                                              |

| 2.8 Error Detection and C                                                                                                                                                | orrection                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| <ul> <li>If no bits are lost or corrupted,<br/>dividing the received<br/>information string by the<br/>agreed upon pattern will give a<br/>remainder of zero.</li> </ul> | $\frac{1011011}{1101}$ $\frac{1101}{001010}$     |

| <ul> <li>We see this is so in the<br/>calculation at the right.</li> </ul>                                                                                               | $\frac{1101}{01111}$                             |

| <ul> <li>Real applications use longer<br/>polynomials to cover larger<br/>information strings.</li> </ul>                                                                | $\frac{\frac{1101}{001011}}{\frac{1101}{01101}}$ |

| <ul> <li>Some of the standard poly-<br/>nomials are listed in the text.</li> </ul>                                                                                       | $\frac{1101}{0000}$                              |

|                                                                                                                                                                          | 101                                              |

- Data transmission errors are easy to fix once an error is detected.

- Just ask the sender to transmit the data again.

- In computer memory and data storage, however, this cannot be done.

- Too often the only copy of something important is in memory or on disk.

- Thus, to provide data integrity over the long term, error *correcting* codes are required.

- Hamming codes and Reed-Soloman codes are two important error correcting codes.

- Reed-Soloman codes are particularly useful in correcting *burst errors* that occur when a series of adjacent bits are damaged.

- Because CD-ROMs are easily scratched, they employ a type of Reed-Soloman error correction.

- Because the mathematics of Hamming codes is much simpler than Reed-Soloman, we discuss Hamming codes in detail.

# 2.8 Error Detection and Correction

- Hamming codes are code words formed by adding redundant check bits, or parity bits, to a data word.

- The *Hamming distance* between two code words is the number of bits in which two code words differ.

This pair of bytes has a1 0 0 0 1 0 0 1Hamming distance of 3:1 0 1 1 0 0 0 1

• The minimum Hamming distance for a code is the smallest Hamming distance between *all* pairs of words in the code.

# 2.8 Error Detection and Correction

- The minimum Hamming distance for a code, D(min), determines its error detecting and error correcting capability.

- For any code word, *X*, to be interpreted as a different valid code word, *Y*, at least D(min) single-bit errors must occur in *X*.

- Thus, to detect k (or fewer) single-bit errors, the code must have a Hamming distance of D(min) = k + 1.

103

Hamming codes can detect D(min) - 1 errors and correct | D(Min) - 1 | errors

- Thus, a Hamming distance of 2*k* + 1 is required to be able to correct *k* errors in any data word.

- Hamming distance is provided by adding a suitable number of parity bits to a data word.

# 2.8 Error Detection and Correction

- Suppose we have a set of *n*-bit code words consisting of *m* data bits and *r* (redundant) parity bits.

- An error could occur in any of the *n* bits, so each code word can be associated with *n* erroneous words at a Hamming distance of 1.

- Therefore, we have *n* + 1 bit patterns for each code word: one valid code word, and *n* erroneous words.

107

106

# 2.8 Error Detection and Correction

With *n*-bit code words, we have 2<sup>n</sup> possible code words consisting of 2<sup>m</sup> data bits (where m = n + r).

n

· This gives us the inequality:

$$(n + 1) \times 2^{m} \le 2$$

• Because *m* = *n* + *r*, we can rewrite the inequality as:

$(m + r + 1) \times 2^{m} \le 2^{m+r}$  or  $(m + r + 1) \le 2^{r}$

- This inequality gives us a lower limit on the number of check bits that we need in our code words.

• Suppose we have data words of length *m* = 4. Then:

$$(4 + r + 1) \le 2^r$$

implies that r must be greater than or equal to 3.

- This means to build a code with 4-bit data words that will correct single-bit errors, we must add 3 check bits.

- Finding the number of check bits is the hard part. The rest is easy.

# 2.8 Error Detection and Correction

• Suppose we have data words of length *m* = 8. Then:

$(8 + r + 1) \le 2^r$

implies that r must be greater than or equal to 4.

- This means to build a code with 8-bit data words that will correct single-bit errors, we must add 4 check bits, creating code words of length 12.

- So how do we assign values to these check bits?

### 110

109

# 2.8 Error Detection and Correction

• With code words of length 12, we observe that each of the digits, 1 though 12, can be expressed in powers of 2. Thus:

$\begin{array}{ll} 1 = 2^{0} & 5 = 2^{2} + 2^{0} & 9 = 2^{3} + 2^{0} \\ 2 = 2^{1} & 6 = 2^{2} + 2^{1} & 10 = 2^{3} + 2^{1} \\ 3 = 2^{1} + 2^{0} & 7 = 2^{2} + 2^{1} + 2^{0} & 11 = 2^{3} + 2^{1} + 2^{0} \end{array}$

$4 = 2^{2}$   $8 = 2^{3}$   $12 = 2^{3} + 2^{2}$

$-1 (= 2^0)$  contributes to all of the odd-numbered digits.

$-2 (= 2^{1})$  contributes to the digits, 2, 3, 6, 7, 10, and 11.

• We can use this idea in the creation of our check bits.

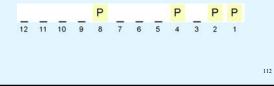

- Using our code words of length 12, number each bit position starting with 1 in the low-order bit.

- Each bit position corresponding to an even power of 2 will be occupied by a check bit.

- These check bits contain the parity of each bit position for which it participates in the sum.

### 2.8 Error Detection and Correction • Since 2 (= 2<sup>1</sup>) contributes to the digits, 2, 3, 6, 7, 10, and 11. Position 2 will contain the parity for bits 3, 6, 7, 10, and 11. • When we use even parity, this is the modulo 2 sum of the participating bit values. • For the bit values shown, we have a parity value of 0 in the second bit position. 1 1 0 1 0 1 1 0 0 12 11 10 9 8 7 6 5 4 3 2 1 What are the values for the other parity bits? 113

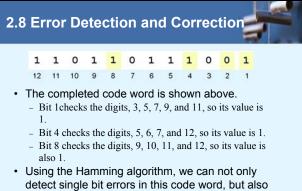

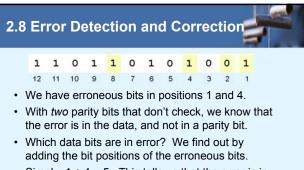

detect single bit errors in this code word, but als correct them!

1 1 0 0 1 0 1 0 0 1 1 12 11 10 9 8 6 5 4 3 2 7

- Suppose an error occurs in bit 5, as shown above. Our parity bit values are:

- Bit 1 checks digits, 3, 5, 7, 9, and 11. Its value is 1, but should be zero.

- Bit 2 checks digits 2, 3, 6, 7, 10, and 11. The zero is correct.

- Bit 4 checks digits, 5, 6, 7, and 12. *Its value is 1, but should be zero.*

- Bit 8 checks digits, 9, 10, 11, and 12. This bit is correct.

• Simply, 1 + 4 = 5. This tells us that the error is in bit 5. If we change bit 5 to a 1, all parity bits check and our data is restored.

# **Chapter 2 Conclusion**

- Computers store data in the form of bits, bytes, and words using the binary numbering system.

- Hexadecimal numbers are formed using four-bit groups called nibbles (or nybbles).

- Signed integers can be stored in one's complement, two's complement, or signed magnitude representation.

- Floating-point numbers are usually coded using the IEEE 754 floating-point standard.

115

# **Chapter 2 Conclusion**

- Character data is stored using ASCII, EBCDIC, or Unicode.

- Data transmission and storage codes are devised to convey or store bytes reliably and economically.

- Error detecting and correcting codes are necessary because we can expect no transmission or storage medium to be perfect.

- CRC, Reed-Soloman, and Hamming codes are three important error control codes.

# **Chapter 6 Objectives**

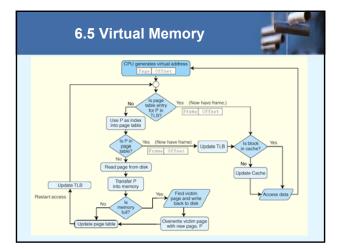

- Master the concepts of hierarchical memory organization.

- Understand how each level of memory contributes to system performance, and how the performance is measured.

- Master the concepts behind cache memory, virtual memory, memory segmentation, paging and address translation.

# **6.1 Introduction**

-

- Memory lies at the heart of the stored-program computer.

- In previous chapters, we studied the components from which memory is built and the ways in which memory is accessed by various ISAs.

- In this chapter, we focus on memory organization. A clear understanding of these ideas is essential for the analysis of system performance.

### 6.2 Types of Memory

- There are two kinds of main memory: random access memory, RAM, and read-only-memory, ROM.

- There are two types of RAM, dynamic RAM (DRAM) and static RAM (SRAM).

- Dynamic RAM consists of capacitors that slowly leak their charge over time. Thus they must be refreshed every few milliseconds to prevent data loss.

- DRAM is "cheap" memory owing to its simple design.

# 6.2 Types of Memory

4

- SRAM consists of circuits similar to the D flip-flop that we studied in Chapter 3.

- SRAM is very fast memory and it doesn't need to be refreshed like DRAM does. It is used to build cache memory, which we will discuss in detail later.

- ROM also does not need to be refreshed, either. In fact, it needs very little charge to retain its memory.

- ROM is used to store permanent, or semipermanent data that persists even while the system is turned off.

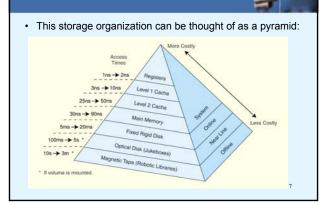

# 6.3 The Memory Hierarchy

- Generally speaking, faster memory is more expensive than slower memory.

- To provide the best performance at the lowest cost, memory is organized in a hierarchical fashion.

- Small, fast storage elements are kept in the CPU, larger, slower main memory is accessed through the data bus.

- Larger, (almost) permanent storage in the form of disk and tape drives is still further from the CPU.

# 6.3 The Memory Hierarchy

# 6.3 The Memory Hierarchy

9

- To access a particular piece of data, the CPU first sends a request to its nearest memory, usually cache.

- If the data is not in cache, then main memory is queried. If the data is not in main memory, then the request goes to disk.

- Once the data is located, then the data, and a number of its nearby data elements are fetched into cache memory.

# 6.3 The Memory Hierarchy

- A hit is when data is found at a given memory level.

- A miss is when it is not found.

- The *hit rate* is the percentage of time data is found at a given memory level.

- The miss rate is the percentage of time it is not.

- Miss rate = 1 hit rate.

- The *hit time* is the time required to access data at a given memory level.

- The *miss penalty* is the time required to process a miss, including the time that it takes to replace a block of memory plus the time it takes to deliver the data to the processor.

### 6.3 The Memory Hierarchy

- An entire blocks of data is copied after a hit because the *principle of locality* tells us that once a byte is accessed, it is likely that a nearby data element will be needed soon.

- There are three forms of locality:

- *Temporal locality* Recently-accessed data elements tend to be accessed again.

- Spatial locality Accesses tend to cluster.

- *Sequential locality* Instructions tend to be accessed sequentially.

### 6.4 Cache Memory

11

10

- The purpose of cache memory is to speed up accesses by storing recently used data closer to the CPU, instead of storing it in main memory.

- Although cache is much smaller than main memory, its access time is a fraction of that of main memory.

- Unlike main memory, which is accessed by address, cache is typically accessed by content; hence, it is often called *content addressable memory*.

- Because of this, a single large cache memory isn't always desirable-- it takes longer to search.

# 6.4 Cache Memory

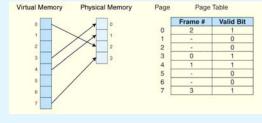

- The "content" that is addressed in content addressable cache memory is a subset of the bits of a main memory address called a *field*.

- The fields into which a memory address is divided provide a many-to-one mapping between larger main memory and the smaller cache memory.

- Many blocks of main memory map to a single block of cache. A *tag* field in the cache block distinguishes one cached memory block from another.

13

14

- The simplest cache mapping scheme is *direct* mapped cache.

- In a direct mapped cache consisting of N blocks of cache, block X of main memory maps to cache block Y = X mod N.

- Thus, if we have 10 blocks of cache, block 7 of cache may hold blocks 7, 17, 27, 37, . . . of main memory.

- Once a block of memory is copied into its slot in cache, a *valid* bit is set for the cache block to let the system know that the block contains valid data.

What could happen without having a valid bit?

# 6.4 Cache Memory

The diagram below is a schematic of what cache looks like. Block Tag Data Valid

| 0 | 00000000 | words A, B, C, | 1 |

|---|----------|----------------|---|

| 1 | 11110101 | words L, M, N, | 1 |

| 2 |          |                | 0 |

| 3 |          |                | 0 |

- Block 0 contains multiple words from main memory, identified with the tag 00000000. Block 1 contains words identified with the tag 11110101.

- · The other two blocks are not valid.

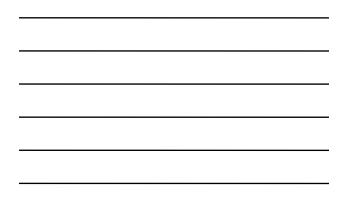

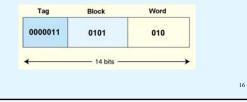

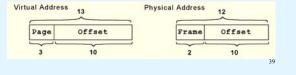

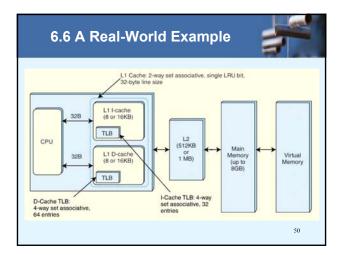

### 6.4 Cache Memory • The size of each field into which a memory address is divided depends on the size of the cache. • Suppose our memory consists of 2<sup>14</sup> words, cache has $16 = 2^4$ blocks, and each blocks. - Thus memory is divided into $2^{14} / 2^{14}$ blocks. • For our field sizes, we know we need 4 bits for the block, 3 bits for the word, and the tag is what's left over: 7 bits 4 bits 3 bits Word Tag Block - 14 bits -15

- As an example, suppose a program generates the address 1AA. In 14-bit binary, this number is: 00000110101010.

- The first 7 bits of this address go in the tag field, the next 4 bits go in the block field, and the final 3 bits indicate the word within the block.

# 6.4 Cache Memory

If subsequently the program generates the address **1AB**, it will find the data it is looking for in block **0101**, word **011**.

| Block | Word   |  |

|-------|--------|--|

| 0101  | 010    |  |

|       | 000000 |  |

However, if the program generates the address, **3AB**, instead, the block loaded for address **1AA**  would be evicted from the cache, and replaced by the blocks associated with the **3AB** reference.

# 6.4 Cache Memory

- The theoretical advantage offered by the cache is lost in this extreme case.

- This is the main disadvantage of direct mapped cache.

- Other cache mapping schemes are designed to prevent this kind of thrashing.

- Instead of placing memory blocks in specific cache locations based on memory address, we could allow a block to go anywhere in cache.

- In this way, cache would have to fill up before any blocks are evicted.

- This is how *fully associative* cache works.

- A memory address is partitioned into only two fields: the tag and the word.

# 6.4 Cache Memory

Suppose, as before, we have 14-bit memory addresses and a cache with 16 blocks, each block of size 8. The field format of a memory reference is:

| Tag | Word |

|-----|------|

|     |      |

- When the cache is searched, all tags are searched in parallel to retrieve the data quickly.

- This requires special, costly hardware.

# 6.4 Cache Memory

- You will recall that direct mapped cache evicts a block whenever another memory reference needs that block.

- With fully associative cache, we have no such mapping, thus we must devise an algorithm to determine which block to evict from the cache.

- The block that is evicted is the victim block.

- There are a number of ways to pick a victim, we will discuss them shortly.

19

- Set associative cache combines the ideas of direct mapped cache and fully associative cache.

- An *N*-way set associative cache mapping is like direct mapped cache in that a memory reference maps to a particular location in cache.

- Unlike direct mapped cache, a memory reference maps to a set of several cache blocks, similar to the way in which fully associative cache works.

- Instead of mapping anywhere in the entire cache, a memory reference can map only to the subset of cache slots.

22

# 6.4 Cache Memory

- The number of cache blocks per set in set associative cache varies according to overall system design.

- For example, a 2-way set associative cache can be conceptualized as shown in the schematic below.

- Each set contains two different memory blocks.

| Set | Tag      | Block 0 of set | Valid | Tag      | Block 1 of set | Valid |

|-----|----------|----------------|-------|----------|----------------|-------|

| 0   | 00000000 | Words A, B, C, | 1     |          |                | 0     |

| 1   | 11110101 | Words L, M, N, | 1     |          |                | 0     |

| 2   |          |                | 0     | 10111011 | P, Q, R,       | 1     |

| 3   |          |                | 0     | 11111100 | T. U. V        | 1     |

# 6.4 Cache Memory

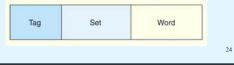

- In set associative cache mapping, a memory reference is divided into three fields: tag, set, and word, as shown below.

- As with direct-mapped cache, the word field chooses the word within the cache block, and the tag field uniquely identifies the memory address.

- The set field determines the set to which the memory block maps.

- Suppose we have a main memory of 2<sup>14</sup> bytes.

- This memory is mapped to a 2-way set associative cache having 16 blocks where each block contains 8 words.

- Since this is a 2-way cache, each set consists of 2 blocks, and there are 8 sets.

- Thus, we need 3 bits for the set, 3 bits for the word, giving 8 leftover bits for the tag:

|     | 3 bits  | 3 bits |

|-----|---------|--------|

| Tag | Set     | Word   |

|     | 14 bits |        |

# 6.4 Cache Memory

- With fully associative and set associative cache, a replacement policy is invoked when it becomes necessary to evict a block from cache.

- An optimal replacement policy would be able to look into the future to see which blocks won't be needed for the longest period of time.

- Although it is impossible to implement an optimal replacement algorithm, it is instructive to use it as a benchmark for assessing the efficiency of any other scheme we come up with.

# 6.4 Cache Memory

- The replacement policy that we choose depends upon the locality that we are trying to optimize-usually, we are interested in temporal locality.

- A least recently used (LRU) algorithm keeps track of the last time that a block was assessed and evicts the block that has been unused for the longest period of time.

- The disadvantage of this approach is its complexity: LRU has to maintain an access history for each block, which ultimately slows down the cache.

- In FIFO, the block that has been in the cache the longest, regardless of when it was last used.

- A random replacement policy does what its name implies: It picks a block at random and replaces it with a new block.

- Random replacement can certainly evict a block that will be needed often or needed soon, but it never thrashes.

# 6.4 Cache Memory