### **Karnaugh Map POS Minimization**

In this section, we will focus on POS expressions instead of SOP. The approaches are much the same except that with POS expressions, 0's representing the standard sum terms are placed on the karnaugh map instead of 1's.

**Example:** Map the following POS expression on a karnaugh map.

$$(\overline{A} + \overline{B} + C + D)(\overline{A} + B + \overline{C} + \overline{D})(A + B + \overline{C} + D)(\overline{A} + \overline{B} + \overline{C} + \overline{D})(A + B + \overline{C} + \overline{D})$$

1100 1011 0010 1111 0011

$$\overline{A} + \overline{B} + \overline{C} + \overline{D}$$

$$\overline{A} + B + \overline{C} + \overline{D}$$

**Example:** Use a karnaugh map to minimize the POS expression:

$$(A+B+C)(A+B+\overline{C})(A+\overline{B}+\overline{C})(A+\overline{B}+\overline{C})(\overline{A}+\overline{B}+\overline{C})$$

$$Out = A(\overline{B} + C)$$

keep in mind that this minimum POS expression is equivalent to the original standard POS expression grouping the 1's as shown yields a SOP expression that is equivalent to grouping the 0's.

$$\begin{array}{c|cccc}

\overline{C} & C \\

\hline

AB & 0 & 0 \\

\hline

AB & 0 & 0 \\

\hline

AB & 0 & 1 \\

\hline

AB & 0 & 1 \\

\hline

AB & 1 & 1

\end{array}$$

$$\overline{AC + A\overline{B}} = A(\overline{B} + C)$$

# Review Questions:

1. Use a Karnaugh map to minimize the POS expression:

$$(B+C+D)(A+B+\overline{C}+D)(\overline{A}+B+C+\overline{D})(A+\overline{B}+C+D)(\overline{A}+\overline{B}+C+D)$$

2. Map the following SOP expression on a karnaugh map:

$$\overline{BC} + A\overline{B} + AB\overline{C} + A\overline{B}C\overline{D} + \overline{ABC}D + A\overline{B}CD$$

- 3. What is the difference in mapping a POS expression and an SOP expression?

- 4. What is the standard sum term for a 0 in cell 1011?

- 5. What is the standard product term for a 1 in cell 0010?

- 6. Determine the minimum expression for each K-map in figure below:

|                 | $\overline{C}\overline{D}$ | $\overline{C}D$ | CD | $C\overline{D}$ |

|-----------------|----------------------------|-----------------|----|-----------------|

| $\overline{AB}$ | 1                          | 1               | 1  | 1               |

| $\overline{A}B$ | 1                          | 1               | 0  | 0               |

| AB              | 0                          | 0               | 0  | 1               |

| $A\overline{B}$ | 0                          | 1               | 1  | 0               |

|                            | CD | CD | CD | CD |

|----------------------------|----|----|----|----|

| $\overline{A}\overline{B}$ | 1  | 0  | 1  | 1  |

| $\overline{A}B$            | 1  | 0  | 0  | 1  |

| AB                         | 0  | 0  | 0  | 0  |

| $A\overline{B}$            | 1  | 0  | 1  | 1  |

7. Use a K-map to simplify each expression to a minimum SOP form:

(a)

$$\overline{A}\overline{B}\overline{C} + A\overline{B}C + \overline{A}BC + AB\overline{C}$$

Ans:No Simplifica tion

(b)

$$AC[\overline{B} + B(B + \overline{C})]$$

Ans:AC

(c)

$$DE\overline{F} + \overline{D}E\overline{F} + \overline{D}\overline{E}F$$

$Ans: \overline{D}\overline{F} + E\overline{F}$

8. Reduce the function specified in the truth table in figure below to its minimum SOP form by using K-map.  $A \mid B \mid C \mid X$

Ans:  $\overline{B} + C$

| A | В | C | X |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

9. Use a k-map to simplify each expression to a minimum POS form:

(a)

$$(A + \overline{B} + C + \overline{D})(\overline{A} + B + \overline{C} + D)(\overline{A} + \overline{B} + \overline{C} + \overline{D})$$

(b)

$$(X + \overline{Y})(W + \overline{Z})(\overline{X} + \overline{Y} + \overline{Z})(W + X + Y + Z)$$

- 10. Simplify the following equation:  $f(A, B, C, D) = \sum (1,3,7,11,15)$ .

- 11. Simplify the following equation:

$$f(A,B,C,D) = \sum (1,5,6,11,14,15)$$

dm(2,3,7) where dm is denoted for don't care.

# **Implementation of Logic Circuit:**

In this section, several general examples are used to illustrate how to implement a logic circuit from a Boolean expression or a truth table.

## 1- From Boolean Expression to a Circuit:

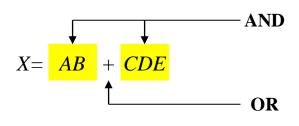

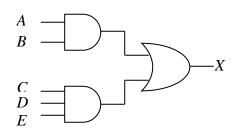

The following expression is the first in the series of examples that will be considered:- X=AB+CDE

This expression is composed of two terms, AB and CDE, with a total of five variables. The first term is formed by ANDing A with B, and the second term is formed by ANDing C, D, and E. The two terms are then ORed to form the output X. These operations are indicated in the structure of the expression as follows:

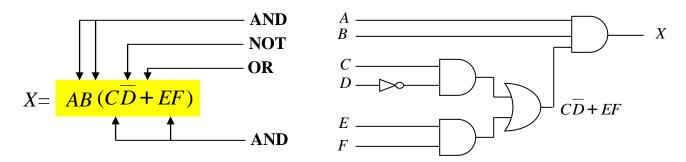

**Example:** Implement the following expression:  $X = AB(C\overline{D} + EF)$

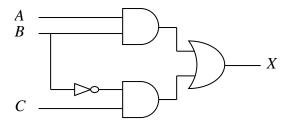

**Example:** Draw the circuit diagram that implements the expression:  $X = AB + \overline{B}C$

## 2- From Truth Table to a Circuit:

Beginning with a truth table, we will write the SOP expression from the truth table and then implement the logic circuit. The table below specifies a logic function. The expression is obtained from a truth table by ORing the product terms for all occurrences of X=1. The expression is:  $X = \overline{ABC} + A\overline{BC}$

|   | Input | Output |   |

|---|-------|--------|---|

| A | В     | С      | X |

| 0 | 0     | 0      | 0 |

| 0 | 0     | 1      | 0 |

| 0 | 1     | 0      | 0 |

| 0 | 1     | 1      | 1 |

| 1 | 0     | 0      | 1 |

| 1 | 0 | 1 | 0 |

|---|---|---|---|

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

The logic gates required to implement this expression are as follows:

Three inverters to form the  $\overline{A}$ ,  $\overline{B}$  and  $\overline{C}$ variables; two 3-input AND gates to form the term ABC and ABC; and one 2-input OR gate to form the final output.

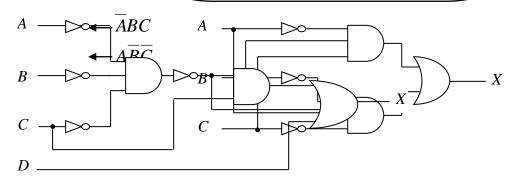

**Example:** Reduce the combination

form:

The expression for the output of the circuit is:  $X = (\overline{A}\overline{B}\overline{C})C + \overline{A}\overline{B}\overline{C} + D$

Applying DeMorgan's theorem and Boolean algebra:

$$X = (\overline{A} + \overline{B} + \overline{C})C + \overline{A} + \overline{B} + \overline{C} + D$$

=  $AC + BC + CC + A + B + C + D = AC + BC + C + A + B + C + D$

=  $C(A + B + 1 + 1) + A + B + D = A + B + C + D$

Hence, the simplified circuit is a **4-input OR gate**.

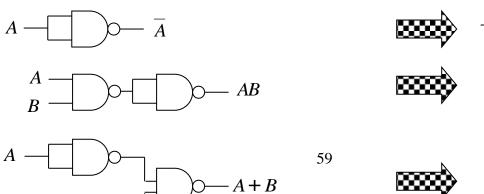

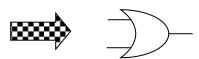

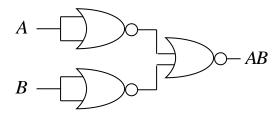

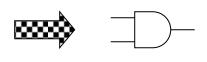

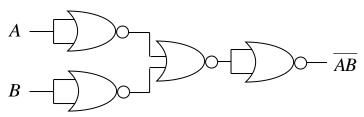

# **Universal Property of NAND and NOR Gates:**

Up to this point, combinational circuits implemented with AND gates, OR gates and inverters have been studied. In this section, the universal property of the NAND gate and the NOR gate is introduced, the universality of the NAND gate means that it can be used as an inverter and that combinations of NAND gates can be used to implement the AND, OR and NOR operations. Similarly, the NOR gate can be used to implement the inverter, AND, OR and NAND operations.

#### 1- <u>Using NAND Gate:</u>

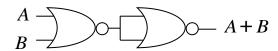

# 2- Using NOR Gate:

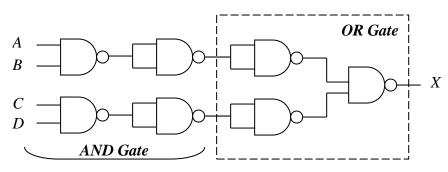

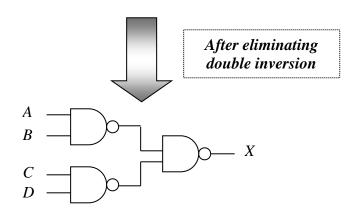

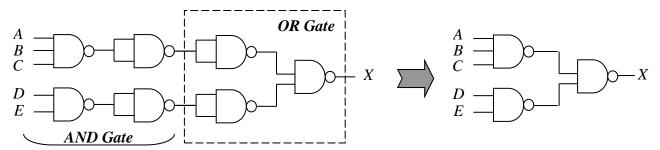

**Example:** Design using NAND gates the following expression: X = AB + CD

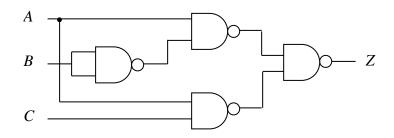

**Example:** Design  $Z = AC + A\overline{B}$  using NAND gates only:

$$Z = \overline{\overline{AC} + A\overline{B}} = \overline{\overline{AC}.\overline{AB}}$$

(Conversion to Product form)

**Example:** Design  $Z = AC + A\overline{B}$  using NOR gates only:

$$Z = \overline{\overline{AC}} + \overline{\overline{AB}} = (\overline{\overline{A} + \overline{C}}) + (\overline{\overline{A} + B})$$

(Conversion to Sum form)

**Example:** Implement the following expression with NAND gates only: ABC + DE

**Example:** Implement the logic circuit that has the expression  $X = \overline{AB.(\overline{C+D})}$  using only one NAND and NOR gate.

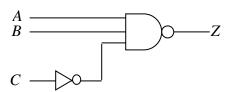

**Example:** Implement a circuit having the output expression  $Z = \overline{A} + \overline{B} + C$  using only one NAND and an inverter gate.

$$Z = \overline{A} + \overline{B} + C$$

can be written as:

$Z = \overline{A.B.C} = \overline{A.B.C}$

# Review Questions:

8. Implement the following logic expressions:

(a)

$$X = ABC + AB + AC$$

(b)

$$X = AB(C + DE)$$

(c)

$$X = B(C\overline{D}E + \overline{E}FG)(\overline{AB} + C)$$

(d)

$$X = \overline{ABC} + B(EF + \overline{G})$$

9. Use NAND gates to implement::

(a)

$$X = \overline{A} + B$$

(b)

$$X = A\overline{B}$$

- 10. Implement the expression  $X = (\overline{A} + \overline{B} + \overline{C})DE$  by using NAND logic.

- 11. Implement the expression  $X = \overline{ABC} + (D + E)$  with NOR logic.

- 12. Design a logic circuit to implement the operation specified in the truth table indicated by Table (a):

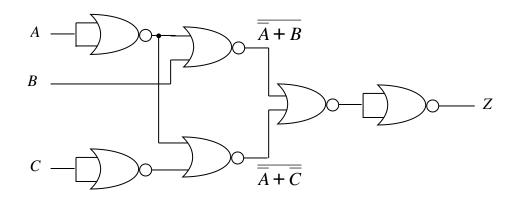

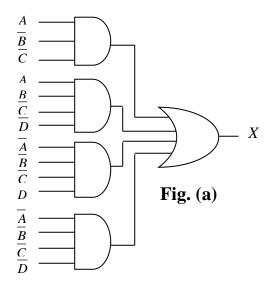

- 13. Minimize the combinational logic circuit shown in Fig. (a):

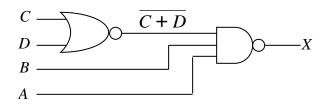

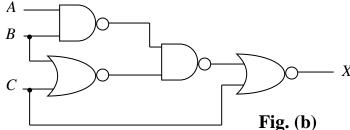

- 14. Implement the logic circuit in Fig. (b) using only NAND gates. Repeat the design using only NOR gates.

Table (a)

|   | Input | Output |   |

|---|-------|--------|---|

| A | В     | C      | X |

| 0 | 0     | 0      | 0 |

| 0 | 0     | 1      | 0 |

| 0 | 1     | 0      | 0 |

| 0 | 1     | 1      | 1 |

| 1 | 0     | 0      | 0 |

| 1 | 0     | 1      | 1 |

| 1 | 1     | 0      | 1 |

| 1 | 1     | 1      | 0 |

15. Show how the following expression can be implemented using only NAND gates:

(a)

$$X = ABC$$

(b)

$$X = \overline{ABC}$$

(c)

$$X = A + B$$

(d)

$$X = A + B + \overline{C}$$

(e)

$$X = \overline{AB} + \overline{CD}$$

(f)

$$X = (A + B)(C + D)$$

(g)

$$X = AB[C(\overline{DE} + \overline{AB}) + \overline{BCE}]$$

16. Implement each function by using only NAND gates:

(a)

$$X = A\overline{B} + AB$$

(b)

$$X = A[BC(A + B + C + D)]$$

17. Minimize the gates required to implement the function in SOP form:

(a)

$$X = A\overline{B} + AB$$

(b)

$$X = \overline{ABC} + B(EF + \overline{G})$$

(c)

$$X = A[BC(A + B + C + D)]$$

(d)

$$X = B(C\overline{D}E + \overline{E}FG)(\overline{AB} + C)$$

- 18. Design a minimal circuit to detect 31-day months, coded in 8-4-2-1 binary.

- 19. Obtain a minimal SOP for the function below then implement using NAND gates only:  $f(A, B, C, D) = \sum_{i=0}^{\infty} (0.7, 8, 10, 12) + d(2, 6, 11)$ .

- 20. Using a karnaugh map, convert the following standard POS expression into a minimum POS expression, a standard SOP expression and a minimum SOP expression:

$$f(A,B,C,D) = \Pi(1,2,3,4,9,12)$$

where  $\Pi$  is denoted for POS

# **Basic Adders:**

Adders are important not only in computers, but in many types of digital systems in which numerical data are processed. An understanding of the basic adder operation is fundamental to the study of digital systems. In this section, the half-adder and the full-adder are introduced.

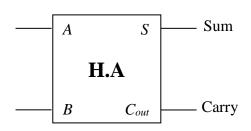

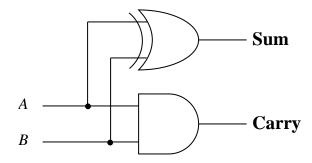

## 3- The Half-Adder (H.A):

Recall the basic rules for binary addition as stated in the previous lectures:

| 0 | + | 0 | = | 0 |

|---|---|---|---|---|

|   |   |   |   |   |

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

These operations are performed by a logic circuit called a half-adder. The half-adder accepts two binary digits on its inputs and produces two binary digits on its outputs, a <u>Sum</u> bit and a <u>Carry</u> bit.

| A | В | $C_{out}$ | S |

|---|---|-----------|---|

| 0 | 0 | 0         | 0 |

| 0 | 1 | 0         | 1 |

| 1 | 0 | 0         | 1 |

| 1 | 1 | 1         | 0 |

$$S = A \oplus B$$

$$C_{out} = AB$$

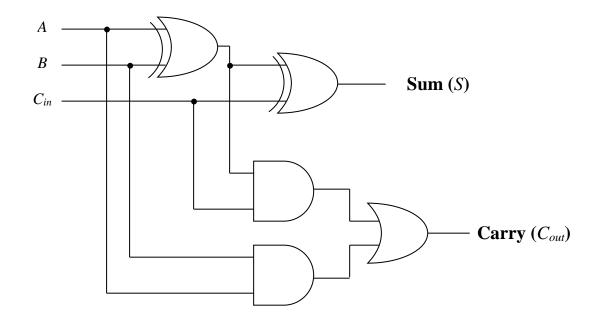

## 4- The Full-Adder(F.A):

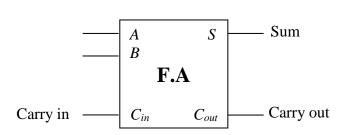

The second basic category of adder is the Full-adder. The full-adder accepts three inputs including an input carry and generates a **Sum** output and output **carry.**

| A | В | $C_{in}$ | $C_{out}$ | S |

|---|---|----------|-----------|---|

| 0 | 0 | 0        | 0         | 0 |

| 0 | 0 | 1        | 0         | 1 |

| 0 | 1 | 0        | 0         | 1 |

| 0 | 1 | 1        | 1         | 0 |

| 1 | 0 | 0 | 0 | 1 |

|---|---|---|---|---|

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

From the truth table:-

$$C_{out} = \overline{ABC}_{in} + A\overline{BC}_{in} + AB\overline{C}_{in} + ABC_{in}$$

$$= (\overline{AB} + A\overline{B})C_{in} + AB$$

$$C_{out} = (A \oplus B)C_{in} + AB \qquad .....Eq.(1)$$

$$S = \overline{ABC}_{in} + \overline{ABC}_{in} + A\overline{BC}_{in} + ABC_{in}$$

$$= \overline{ABC}_{in} + (\overline{AB} + A\overline{B})\overline{C}_{in} + ABC_{in} \qquad ......Eq.(2)$$

$$But \ \overline{ABC}_{in} + ABC_{in} = \overline{(\overline{AB} + AB)}C_{in}$$

$$= (\overline{A + B})(\overline{A} + \overline{B})C_{in}$$

$$= (\overline{AB} + B\overline{A})C_{in} \qquad .....Eq.(3)$$

Substituting Eq.3 in Eq.2

$$S = (\overline{AB} + A\overline{B})\overline{C_{in}} + (\overline{\overline{AB} + A\overline{B}})C_{in} = A \oplus B \oplus C_{in}$$

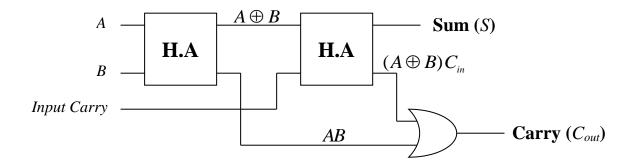

*Example:* Arrange two half-adders to form full-adder.

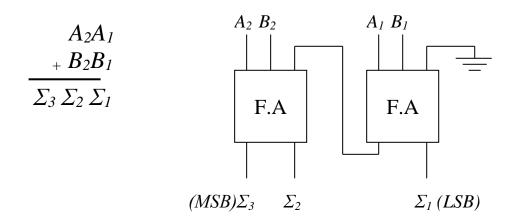

### **Parallel Binary Adders:**

Adders that are available in integrated circuits form are parallel binary adders. As you saw in the previous section, a single full-adder is capable of adding two 1-bit numbers and an input carry. To add binary numbers with more than one bit, additional full-adders must be employed. To implement the addition of binary numbers, a full-adder is required for each bit in the numbers. So, for <u>2-bit</u> numbers, <u>two</u> adders are needed; for <u>4-bit</u> numbers, four adders are used; and so on.