Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

# **Basic Logic Gates**

## **OBJECTIVE**

Understanding the symbols and characteristics of various basic logic gates.

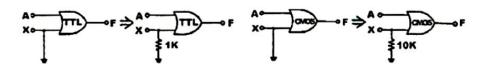

1. OR gate: input of TTL are connected to a 1K resistor while input of CMOS gates are connected to a  $10K\Omega$  resistor.

TTL with  $1K\Omega$  resistor at the input

CMOS with  $10K\Omega$  resistor at the input

Resistance for the LS series TTL is approximately  $5K\Omega$ . If the X input of a TTL OR gate is grounded then the output F is equal to the input A (F=A), making expansion control impossible.

If the resistor is grounded and there is no signal at X, then X is equivalent to being grounded and F=A. If necessary a signal could be added to X so that  $F=A\times X$ . The output can be controlled by X.

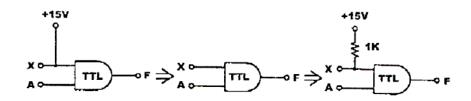

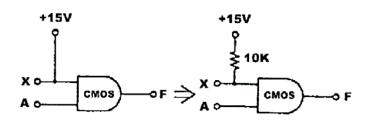

2. AND gate: TTL AND gates are in high state when it is open or when a resistor is connected to the supply voltage. CMOS AND gates are in high state when a resistor of at least  $10K\Omega$  is connected to the supply voltage.

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

"HIGH" TTL AND gate

"HIGH" CMOS AND gate

The "Truth Table" is a table that shows a logic gate's corresponding inputs and outputs under ideal conditions.

# 1. OR gate

| STATE | INPUT |   | OUTPUT |                              |

|-------|-------|---|--------|------------------------------|

|       | Α     | В | F      |                              |

| 0     | 0     | 0 | 0      | When A=0, B=0 the output F=0 |

| 1     | 0     | 1 | 1      | When A=0, B=1 the output F=1 |

| 2     | 1     | 0 | 1      | When A=1, B=0 the output F=1 |

| 3     | 1     | 1 | 1      | When A=1, B=1 the output F=1 |

In Boolean expression,  $F = \overline{A} B + A \overline{B} + AB = A + B$

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

## 2. AND gate

|   | STATE | INPUT |   | OUTPUT |                              |

|---|-------|-------|---|--------|------------------------------|

|   |       | Α     | В | F      |                              |

| • | 0     | 0     | 0 | 0      | When A=0, B=0 the output F=0 |

|   | 1     | 0     | 1 | 0      | When A=0, B=1 the output F=0 |

|   | 2     | 1     | 0 | 0      | When A=1, B=0 the output F=0 |

|   | 3     | 1     | 1 | 1      | When A=1, B=1 the output F=1 |

In Boolean expression, F=AB

### 3. INVERTER gate

| STATE | INPUT | ОИТРИТ |                          |

|-------|-------|--------|--------------------------|

|       | Α     | F      |                          |

| 0     | 0     | 1      | When A=0, the output F=1 |

| 1     | 1     | 0      | When A=1, the output F=0 |

In Boolean expression,  $F=\overline{A}$

## 4. XOR gate

| STATE | INF | TU | OUTPUT |

|-------|-----|----|--------|

|       | Α   | В  | F      |

| 0     | 0   | 0  | 0      |

| 1     | 0   | 1  | 1      |

| 2     | 1   | 0  | 1      |

| 3     | 1   | 1  | 0      |

When A=B, the output F=0 When  $A \neq B$ , the output F=1

In Boolean expression,  $F = AB + A\overline{B} = A \oplus B$

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

# 5. NAND gate

The output of a NAND gate is the exact opposite of an AND gate.

| STATE | INPUT |   | ОИТРИТ |                              |

|-------|-------|---|--------|------------------------------|

|       | Α     | В | F      |                              |

| 0     | 0     | 0 | 1      | When A=0, B=0 the output F=1 |

| 1     | 0     | 1 | 1      | When A=0, B=1 the output F=1 |

| 2     | 1     | 0 | 1      | When A=1, B=0 the output F=1 |

| 3     | 1     | 1 | 0      | When A=1, B=1 the output F=0 |

In Boolean expression,  $F = \overline{AB}$

## 6. NOR gate

The output of a NOR gate is the exact opposite of an OR gate.

| STATE | INPUT |   | ОИТРИТ |                              |

|-------|-------|---|--------|------------------------------|

|       | Α     | В | F      |                              |

| 0     | 0     | 0 | 1      | When A=0, B=0 the output F=1 |

| 1     | 0     | 1 | 0      | When A=0, B=1 the output F=0 |

| _ 2   | 1     | 0 | 0      | When A=1, B=0 the output F=0 |

| 3     | 1     | 1 | 0      | When A=1, B=1 the output F=0 |

In Boolean expression,  $F = \overline{A + B} = \overline{A} \times \overline{B}$

These truth tables are based on "positive" logic where positive voltage represents "1" and negative voltage represents "0". In case negative logic is used the output will be reversed.

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

Compare the truth tables for a positive and a negative OR gate shown below:

| STATE | INF | PUT | OUTPUT | STATE | INF | TU | OUTPUT |

|-------|-----|-----|--------|-------|-----|----|--------|

|       | Α   | В   | F      |       | Ā   | B  | F      |

| 0     | 0   | 0   | 0      | 0     | 1   | 1  | 1      |

| 1     | 0   | 1   | 1      | 1     | 1   | 0  | 0      |

| 2     | 1   | 0   | 1      | 2     | 0   | 1  | 0      |

| 3     | 1   | 1   | 1      | 3     | 0   | 0  | 0      |

Observe the truth table for a negative logic OR gate. It to equivalent to a positive logic AND gate.

### **EQUIPMENTS REQUIRED**

KL-31001 Digital Logic Lab; Module KL-33001; Oscilloscope

### **PROCEDURES**

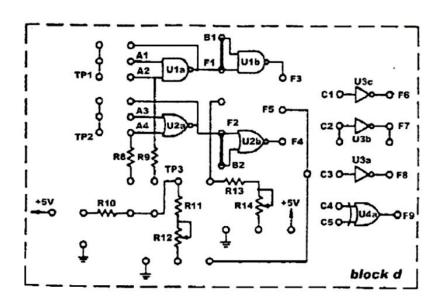

- (a) AND Gate Characteristics Measurement (Module KL-33001 block d)

- 1. Insert connection clips according to Fig. 1-6. U1a and U1b will be used in this section.

- Connect inputs A1, A2 to Data Switch SW0, SW1 TTL level and output F3 to Logic Indicator L0. Follow the input sequences below and record the outputs.

| STATE | INF | PUT | OUTPUT |

|-------|-----|-----|--------|

|       | A2  | A1  | F3     |

| 0     | 0   | 0   |        |

| 1     | 0   | 1   |        |

| 2     | 1   | 0   |        |

| 3     | 1   | 1   |        |

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

Fig. 1-6 STATE

- (b) OR Gate Characteristics Measurement (Module KL-33001 block d)

- 1. U2a and U2b of Module KL-33001 block d will be used in this section.

- 2. Connect inputs A3, A4 to SW0, SW1 TTL level and output F4 to L1. Follow the input sequences below and record output F.

| STATE | INPUT |    | OUTPUT |

|-------|-------|----|--------|

|       | A4    | АЗ | F4     |

| 0     | 0     | 0  |        |

| 1     | 0     | 1  |        |

| 2     | 1     | 0  |        |

| 3     | 1     | 1  |        |

University of Anbar College of Engineering Dept. of Electrical Engineering

Lab. Name: Basic Logic Gates

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

- (c) INVERTER Gate Characteristics Measurement (Module KL-33001 block d)

- 1. U3c of Module KL-33001 block d will be used in this section.

- Connect input C1 and output F6 of U3c to SW0 and L1(LED) respectively.Follow the input sequences below and record outputs.

|   | C1 | F6 |

|---|----|----|

| 0 | 0  |    |

| 1 | 1  |    |

3. Connect F6 to C2 with a test lead. Connect output F7 to L2(LED). Follow the input sequences below and record the outputs.

|   | C2 | F7 |

|---|----|----|

| 0 | 0  |    |

| 1 | 1  |    |

- (d) NAND Gate Characteristics Measurement (Module KL-33001 block d)

- U1a of Module KL-33001 block d will be used in this section. Connect inputs A1, A2 to SW0, SW1 TTL level and output F1 to L1(LED). Follow the input sequences below and record the outputs.

|   | A2 | A1 | F1 |

|---|----|----|----|

| 0 | 0  | 0  |    |

| 1 | 0  | 1  |    |

| 2 | 1  | 0  |    |

| 3 | 1  | 1  |    |

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

- (e) NOR Gate Characteristics Measurement (KL-33001 block d)

- U2a of Module KL-33001 block d will be used in this section. Connect inputs A3, A4 to SW0, SW1 TTL level and output F2 to L1(LED) Follow the input sequences below and record the outputs.

|   | A4 | А3 | F2 |

|---|----|----|----|

| 0 | 0  | 0  |    |

| 1 | 0  | 1  | -  |

| 2 | 1  | 0  |    |

| 3 | 1  | 1  |    |

- (f) XOR Gate Characteristics Measurement (Module KL-33001 block d)

- U4a of Module KL-33001 block d will be used in this section. Connect inputs C4, C5 to SW0, SW1 TTL level and output F9 to L1(LED). Follow the input sequences below and record the outputs.

|   | C5 | C4 | F9 |

|---|----|----|----|

| 0 | 0  | 0  |    |

| 1 | 0  | 1  |    |

| 2 | 1  | 0  |    |

| 3 | 1  | 1  |    |

Experiment no.: 1

Lab. Supervisor: Arrak –M-Idan

## **DISCUSSION:**

- 1- Develop the truth table Four-input NAND gate?

- 2- Develop the truth table Four-input NOR gate?

- 3- Design the logic circuit for the following conditions and draw the output wave form: X is a 0 if any two of the three variable A,B, and C are 1 X is a 1 for all other conditions?

- 4- Improve AB+A(B+C)+B(B+C)=B+AC?

- 5- Define the type of logic gate for each of the following:

- a. 7400

- b. 7404

- c. 7411

- d. 7420

- e. 7432

- f. 7427

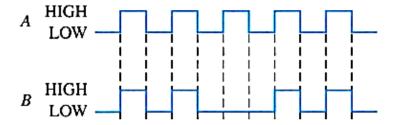

- 6- If two wave forms A and B are applied to the AND gate inputs as in figure whet is the resulting output wave form and draw the X for each of the following?

- a- The OR gate.

- b- The NAND gate.

- c- The NOR gate.

- d- The negative OR gate.