Lab. Name: Electronic I Experiment no.: 7 Lab. Supervisor: Munther N. Thiyab

## **Experiment No.7**

# **The FET Common Source Amplifier**

# <u>Object</u>

The purpose of this experiment is to test the performance of the common source amplifier using the self-bias circuit.

## **Required Parts and Equipment's**

- 1. Electronic Test Board. (M110)

- 2. Dual Polarity Variable DC Power Supply

- 3. Digital Multimeters.

- 4. Dual-Channel Oscilloscope.

- 5. Function Generator.

- 6. N-Channel JFET 2N3823

- 7. Resistors,  $R_5=100K\Omega$ ,  $R_6=10K\Omega$ ,  $R_8=1K\Omega$ ,  $R_7=2.2K\Omega$

#### **Theory**

The common source amplifier configuration is widely used amongst other JFET configurations and can provide both high voltages gain and large input impedance. In this configuration, the input signal is applied to the gate and the output signal is taken from the drain, while the source terminal being the reference or common. In order to work as an amplifier, the JFET should be properly biased by setting the gate-source voltage which results in the required drain current.

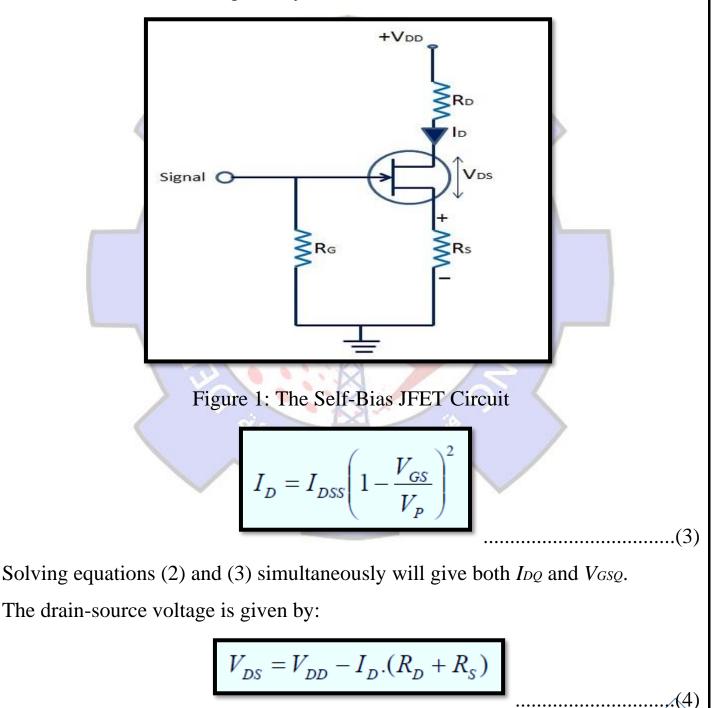

The N-channel JFET requires that the gate-source voltage always be less negative than the pinch-off voltage, but less than zero. Since virtually no gate current flows due to the JFET's high input impedance, the gate voltage is essentially at ground level. Consequently, using only a drain-supply voltage, the required negative quiescent gate-source voltage is developed by the voltage drop across the source resistor of the self-bias circuit shown in Fig.1. This circuit is one of the simplest and practical bias circuits for JFET amplifiers in which a single power supply is used.

Lab. Name: Electronic I Experiment no.: 7 Lab. Supervisor: Munther N. Thiyab

In this circuit, the gate voltage is zero.

Thus, the gate-source voltage is given by:

$$V_{GS} = -I_D R_S....(2)$$

Where the drain current is given by:

Lab. Name: Electronic I Experiment no.: 7 Lab. Supervisor: Munther N. Thiyab

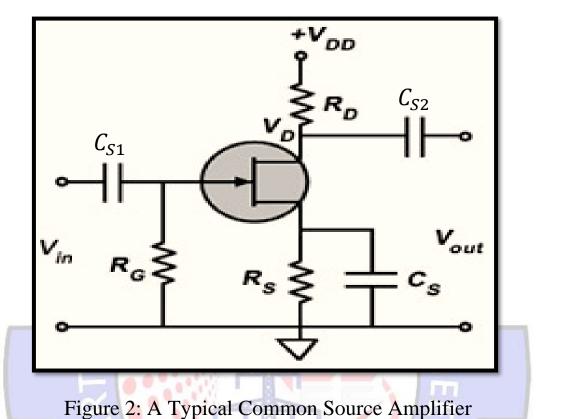

A typical common-source amplifier circuit is shown in Fig.2. In this circuit, capacitors Cc1 and Cc2 are DC blocking capacitors, while Cs is a bypass capacitor for the source resistor Rs.

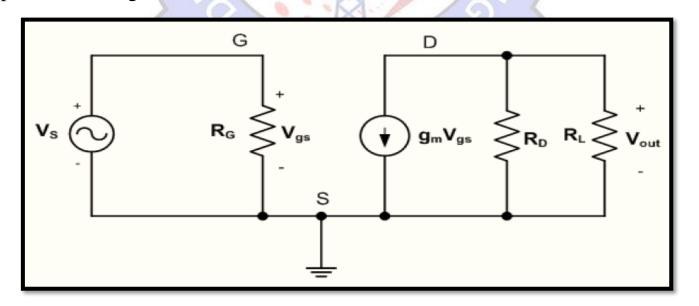

The small-signal approximate equivalent circuit for the amplifier of Fig.2 is presented in Fig.3.

Figure 3: The Simplified Small-Signal Equivalent Circuit of the Amplifier

Lab. Name: Electronic I Experiment no.: 7 Lab. Supervisor: Munther N. Thiyab

(D)

(6)

The transconductance of the JFET at the Q-point is derived as:

$$g_m = \frac{dI_D}{dV_{GS}} \bigg|_{Q-point} = g_{mo} \left( 1 - \frac{V_{GS}}{V_p} \right)$$

(7)

Where g<sub>mo</sub> is given by:

$$g_{mo} = \frac{2I_{DSS}}{\left|V_{p}\right|}$$

The voltage gain of the amplifier can be derived from the equivalent circuit of Fig.4:

$$A_{v} = \frac{V_{out}}{V_{S}} = -g_{m} \cdot (R_{D} \parallel R_{L})$$

It can be shown that when the source bypass capacitor CS is removed, the voltage gain will become:

$$A_{v} = \frac{-g_{m}.(R_{D} || R_{L})}{1 + g_{m}.R_{S}}$$

The input impedance of the amplifier seen from the gate terminal is:

$$Z_{in} = R_G....(9)$$

And the output impedance seen from the output terminals is:

$$Z_{out} = R_D....(10)$$

(8)

Lab. Name: Electronic I Experiment no.: 7 Lab. Supervisor: Munther N. Thiyab

## **Procedure**

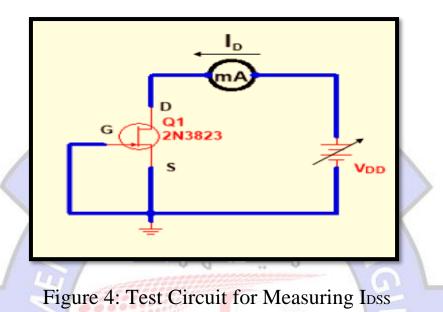

1. Connect the test circuit shown in Fig.4 to measure IDSS. Increase the supply voltage until ID no longer increases. This level of drain current is recorded as IDSS.

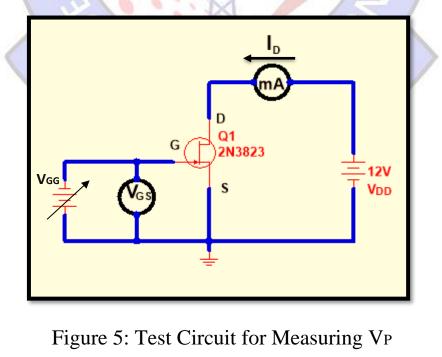

2. Connect the test circuit shown in Fig.5 to measure VP. The gate supply voltage VGG is adjusted from 0 to larger negative values until the drain current ID just reaches 0. The voltage VGs to just cause the drain current to reach 0 is the measured value of VP. Tabulate your results as shown in Table-1.

Lab. Name: Electronic I Experiment no.: 7 Lab. Supervisor: Munther N. Thiyab

#### **Table-1: Measured JFET Parameters**

| <b>Device Parameter</b> | Value |

|-------------------------|-------|

| Idss                    |       |

| VP                      |       |

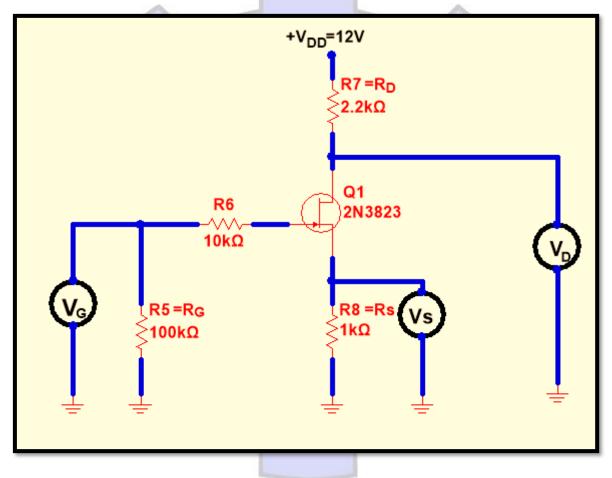

3. Connect the JFET self-bias circuit shown in Fig.6 and measure the DC voltages VG, Vs, and VD with the aid of a digital multi-meter. Determine VGSQ, IDQ, VDSQ, and gm at the Q-point. Tabulate your results as illustrated in Table-2.

Figure 6: The Practical Bias Circuit of the Amplifier

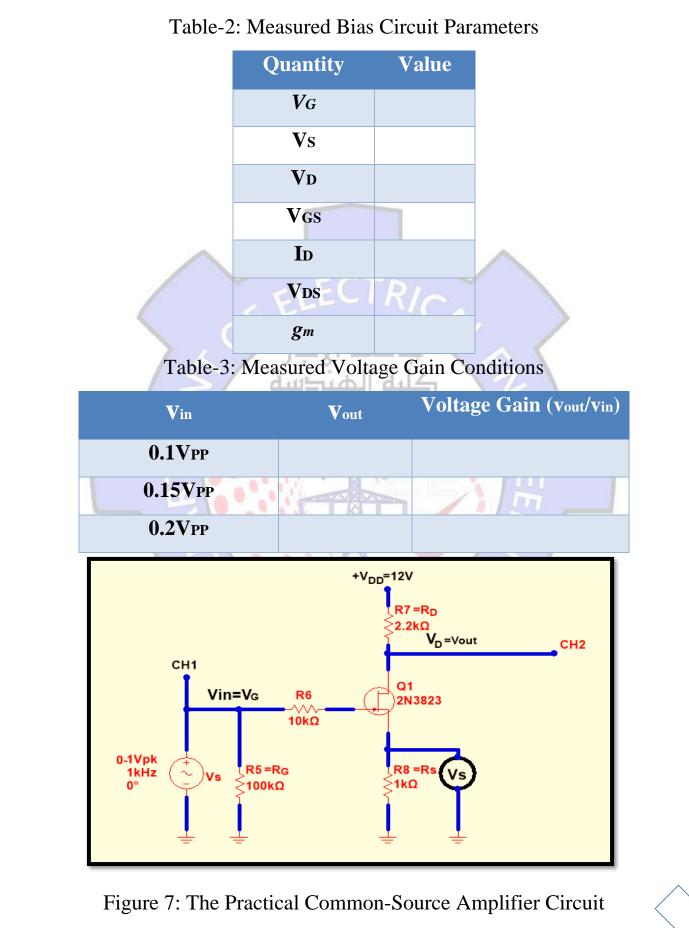

4. Connect the amplifier circuit shown in Fig.7. Sketch the input (Vs) and output (VD) signals and determine the voltage gain of the circuit in three cases as illustrated in Table-3.

Lab. Name: Electronic I Experiment no.: 7 Lab. Supervisor: Munther N. Thiyab

7

#### **Discussion**

- 1. Using the measured device parameters  $I_{DSS}$  and  $V_P$ , calculate the theoretical Q-point values of  $I_{DQ}$  and  $V_{GSQ}$  and compare them with the measured quantities.

- 2. Indicate graphically the effect of increasing the source resistor Rs on the Q-point of the JFET.

- 3. Determine the DC power dissipation in the JFET connected in the amplifier circuit of Fig.7.

- 4. What is the effect of increasing the source resistance RS on the voltage gain of the amplifier circuit?